| Fab Processes                 |                                                                                                                                                                                   |                      |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| - Now we have all of the basi | ic ingredient for an IC Fab:                                                                                                                                                      |                      |  |

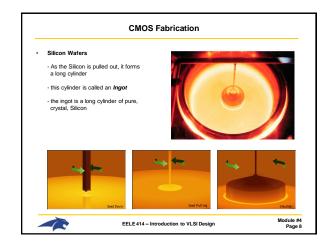

| Silicon Wafer Creation        | <ul> <li>Ingots are grown in crucible starting with a Seed crystal. The ingots<br/>are cut into thin disks and polished to form the Si wafer.</li> </ul>                          |                      |  |

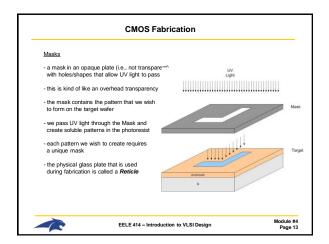

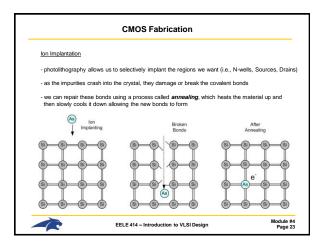

| Photolithography              | <ul> <li>Transferring a pattern to the wafer using masks to selectively expose<br/>regions to UV light with either protect or expose areas on the wafer.</li> </ul>               |                      |  |

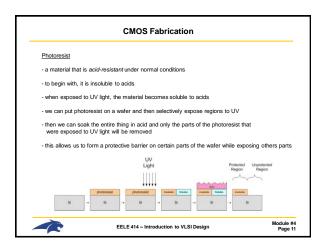

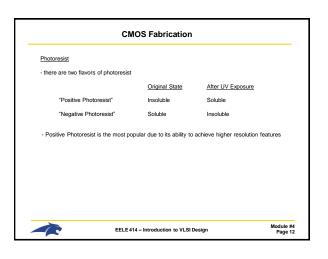

| Photoresist                   | <ul> <li>Normally insoluble material which becomes soluble when exposed<br/>to UV light. The soluble regions can be removed by acid to expose<br/>the regions beneath.</li> </ul> |                      |  |

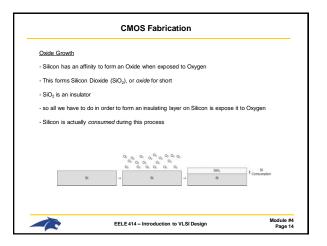

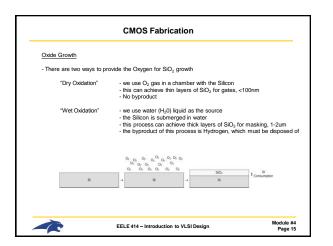

| Oxide Growth                  | <ul> <li>Growing an SiO2 directly on the Silicon wafer using either a Wet or<br/>Dry process. The growth consumes part of the wafer.</li> </ul>                                   |                      |  |

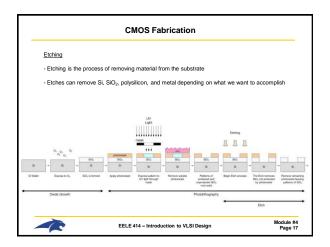

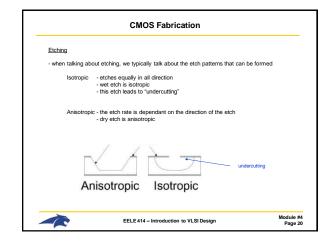

| Etching                       | <ul> <li>process of removing material (Si, SiO<sub>2</sub>, polysilicon, metal) using<br/>either a wet (chemical) or dry (plasma) process.</li> </ul>                             |                      |  |

| Deposition                    | - Process of adding material (SiO <sub>2</sub> , nitride, poly, metal) using CVD/PVD                                                                                              |                      |  |

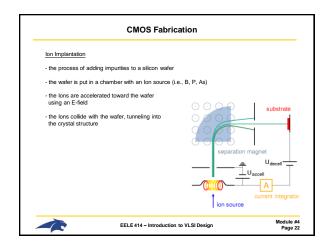

| Ion Implantation              | - Process of adding impurities or doping (ni $\rightarrow$ N_A, N_D)                                                                                                              |                      |  |

|                               |                                                                                                                                                                                   |                      |  |

| À                             | EELE 414 – Introduction to VLSI Design                                                                                                                                            | Module #4<br>Page 24 |  |

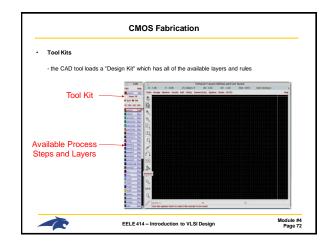

| CMOS Fabric                                                                                                                     | ation                   |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------|

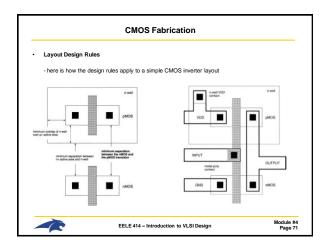

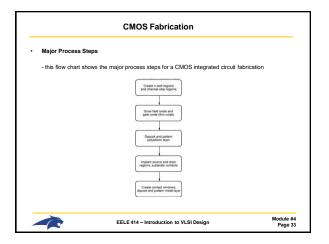

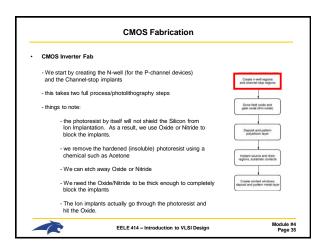

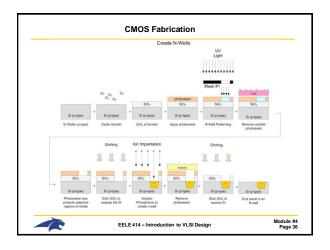

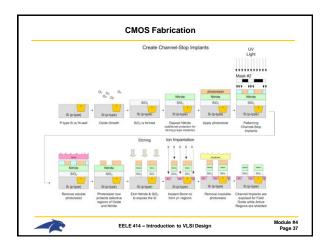

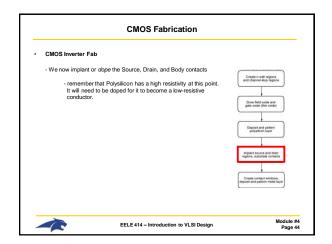

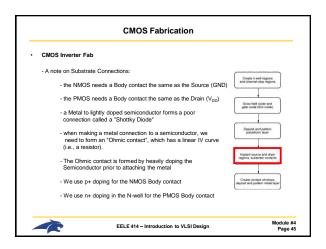

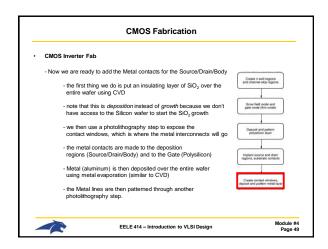

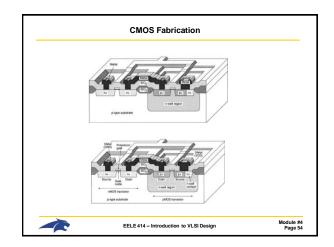

| CMOS Inverter Fab                                                                                                               |                         |

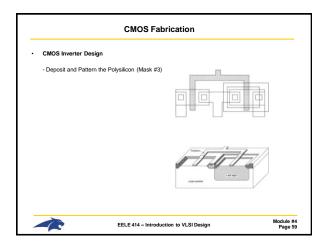

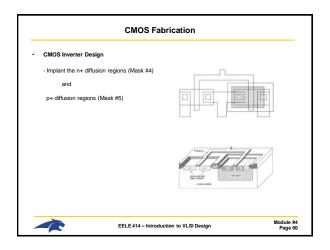

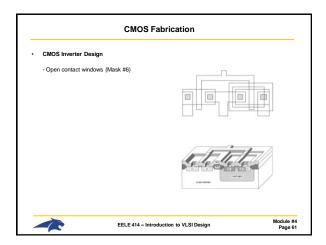

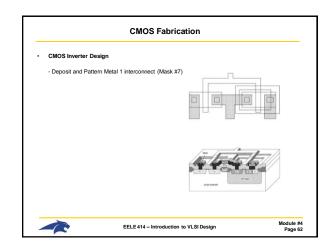

| - Let's review the 7 Mask steps we described in this                                                                            | process:                |

| 1) N-well<br>2) Channel-Stop Implants<br>3) Polysiticon<br>4) n+ Diffusion<br>5) p+ Diffusion<br>6) Contact Windows<br>7) Metal |                         |

| - these 7 mask steps allow us to:                                                                                               |                         |

| - create MOSFETs<br>- connect them together to form basic gates                                                                 |                         |

|                                                                                                                                 |                         |

| EELE 414 – Introduction                                                                                                         | to VLSI Design Module # |

| CMOS Fabrication                            |                                                                                                                      |                   |  |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------|--|--|

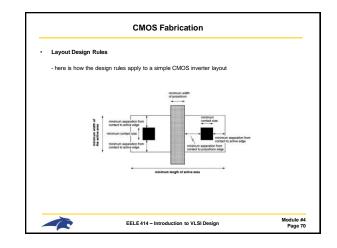

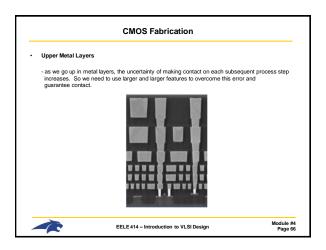

| ayout Design Rules                          |                                                                                                                      |                   |  |  |

| A given fabrication proces<br>process step. | s defines the smallest feature that can be created in                                                                | any given         |  |  |

| It also defines how close t                 | hings can be together                                                                                                |                   |  |  |

| A set of <b>Design Rules</b> are            | edefined for a process that the designers use.                                                                       |                   |  |  |

| Layout rules can be define                  | d in two ways:                                                                                                       |                   |  |  |

| 1) Micron Rules:                            | feature sizes and separations are stated in terms (i.e., 1um, 0.8um)                                                 | of absolute sizes |  |  |

| 2) Lambda Rules:                            | feature sizes and separations are stated in terms called Lambda ( $\lambda$ ). The Lambda rules simplify sc process. |                   |  |  |

|                                             |                                                                                                                      |                   |  |  |

| <u>~</u>                                    | EELE 414 – Introduction to VLSI Desian                                                                               | Module #4         |  |  |