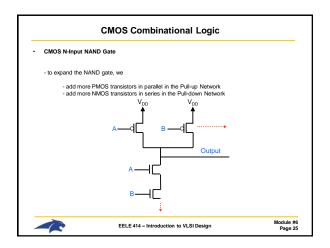

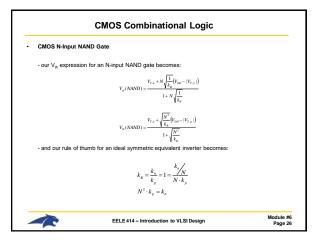

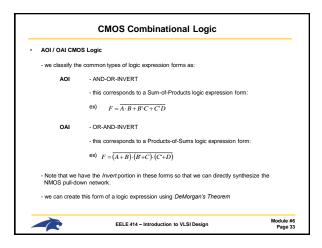

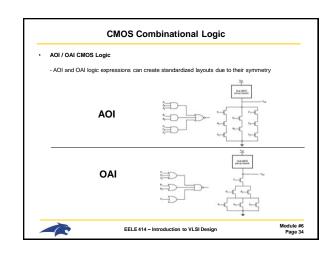

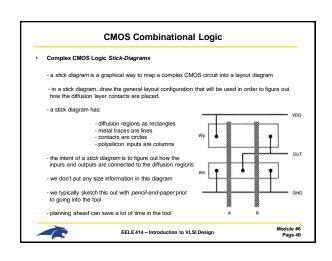

### Module #6 – Combinational Logic • Agenda 1. Combinational Logic - n-Input Gates & Equivalent Inverter - AOI/OAI Logic Synthesis - Transmission Gates - Layout of Complex Logic • Announcements 1. Read Chapter 7

EELE 414 - Introduction to VLSI Design

Module #6 Page 1

## CMOS Basic Gates in CMOS, we always have: a pull-up network using PMOS transistors a pull-down network using NMOS transistors the pull-up and pull-down networks are configured in a complementary topology the complementary topology guarantees that when driving a '1', the pull-up network is ON and the pull-down network is OFF it also guarantees that when driving a '0', the pull-up network is OFF and the pull-down network is ON circuit topology gives us the ability to design logic functionality where transistors: in series = an AND'ing function in parallel = an OR'ing function Module #6 Page 3

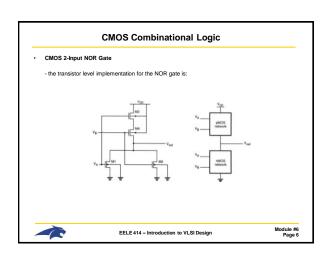

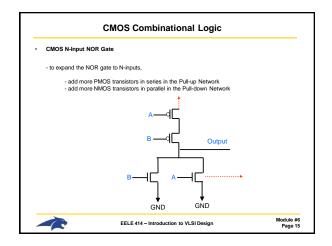

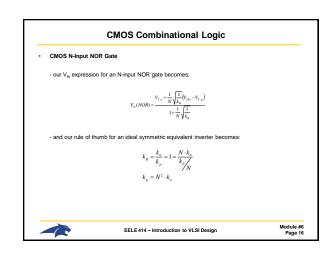

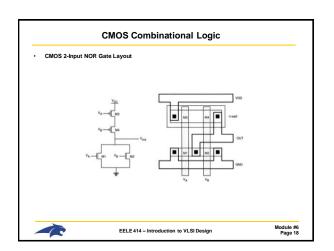

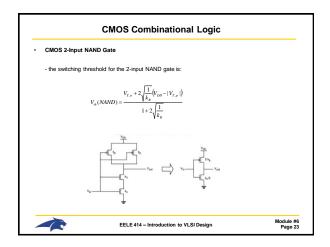

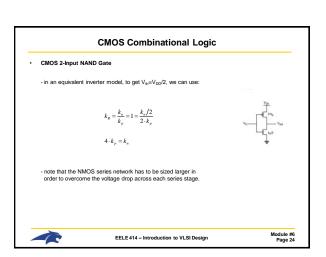

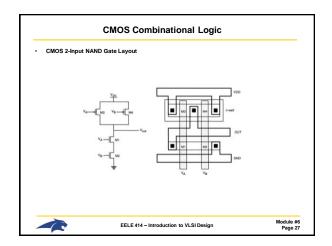

### **CMOS Combinational Logic**

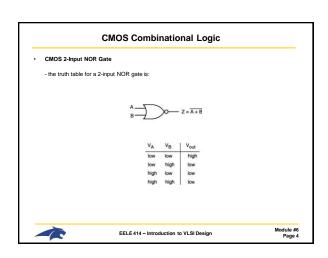

- · CMOS 2-Input NOR Gate

- we have already derived expressions for how to find the critical voltages for an inverter

- of specific interest is V<sub>th</sub>, which we can adjust with the sizing of the transistors

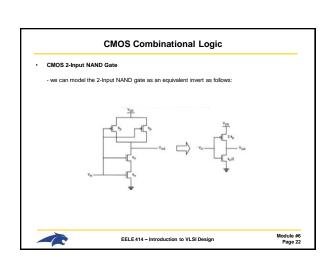

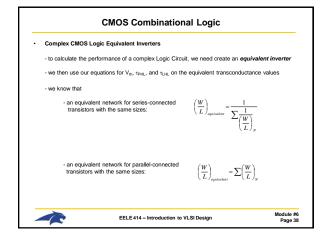

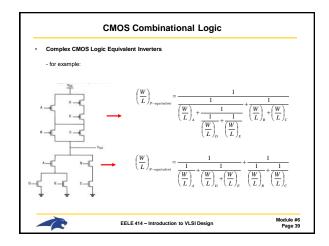

- in order to analyze a more complex logic gate, we convert it into an equivalent inverter

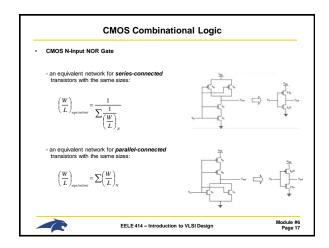

- conceptually, the current flowing in series transistors needs to go through  $\it two$  channels, each with an equivalent resistance (or transconductance  $\it k$ )

- with the effective resistance doubling, we can say that the transconductance (or the ability to drive a current given an input voltage) is divided by 2

- transistors in series with the same size can be modeled as an equivalent transistor with k<sub>en</sub>=k/2

### Transistors in Parallel

- conceptually, the current flowing in parallel transistors can conduct twice the amount of current compared to a a single transistor with the same gate voltage.

- we can model this behavior with an equivalent transistor with  $\mathbf{k}_{eq} \text{=} 2 \cdot \mathbf{k}$

EELE 414 - Introduction to VLSI Design

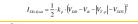

### **CMOS Combinational Logic**

- · CMOS 2-Input NOR Gate

- we can model a 2-Input NOR gate as an equivalent inverter as follows:

- let's use representative voltages of V<sub>DD</sub>=5v and V<sub>th</sub>=2.5 to illustrate the derivation

EELE 414 - Introduction to VLSI Design

### **CMOS Combinational Logic**

- · CMOS 2-Input NOR Gate

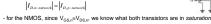

- we can derive the switching threshold by stating that:

$$V_{in} = V_{out} = V_A = V_B = V_{th}$$

- we can begin by writing the KCL equation at the Vout node:

- in addition, we can state that the current at the  $V_{out}$  node is the combination of both NMOS currents

$$I_{\scriptscriptstyle D,n-network} = 2 \cdot I_{\scriptscriptstyle D,n|sat}$$

$$I_{D,a-activork} = 2 \cdot \left[\frac{1}{2} \cdot k_a \cdot \left(V_{ab} - V_{T,a}\right)^2\right] = k_a \cdot \left(V_{tb} - V_{T,s}\right)^2$$

- rearranging this equation to get in terms of  $V_{th}$ , we have:

$$V_{th} = V_{T,n} + \sqrt{\frac{I_{D,n-network}}{k_n}}$$

EELE 414 - Introduction to VLSI Design

### **CMOS Combinational Logic**

- - now we look at the PMOS network, which has a +2.5v drop across it.

- since both transistors are ON, we can estimate that ~1.25v drops across each transistor:

$$V_{_{DS,M3}}=V_{_{DS,M4}}=-1.25\nu$$

- looking at M3, we know that  $V_{GS,p|M3}$ = -2.5v and  $V_{DS,p|M3}$ = -1.25v so M3 is in the linear region.

- looking at M4, the node between M3 and M4 is estimated to be at  $\sim$ 3.75 (i.e., 5v 1.25v)

- this puts V<sub>DS,p|M4</sub>= -1.25v and V<sub>GS,p|M4</sub>= -1.25v, which means M4 is in the saturation region.

EELE 414 - Introduction to VLSI Design

### **CMOS Combinational Logic**

- · CMOS 2-Input NOR Gate

- since we know the regions of operation for M3 and M4, we can write:

$$I_{DS,3lin} = \frac{1}{2} \cdot k_p \cdot \left[ 2 \cdot (V_{GS,p} - V_{T,p}) \cdot V_{DS,p} - V_{DS,p}^2 \right]$$

- Since the PMOS current is expressed terms of  ${\rm I}_{\rm DS},$  we can rewrite this as:

$$\boldsymbol{I}_{DS,n} = \boldsymbol{I}_{SD,p} = -\boldsymbol{I}_{DS,p}$$

- we know that for M3,  $V_{GS,p} = V_{th} - V_{DD}$ . substituting this in and carrying the (-) through, in we get:

$$\begin{split} I_{SD,3lin} &= -I_{DS,3lin} = -\frac{1}{2} \cdot k_p \cdot \left[ 2 \cdot \left( V_{th} - V_{DD} - V_{T,p} \right) \cdot V_{DS,p} - V_{DS,p}^2 \right] \\ I_{SD,3lin} &= \frac{1}{2} \cdot k_p \cdot \left[ 2 \cdot \left( V_{DD} - V_{th} - \left| V_{T,p} \right| \right) \cdot V_{SD,p} - V_{SD,p}^2 \right] \end{split}$$

EELE 414 - Introduction to VLSI Design

### **CMOS Combinational Logic**

- · CMOS 2-Input NOR Gate

- M4 is in the saturation region so we can write the current as:

$$I_{DS,4sat} = \frac{1}{2} \cdot k_p \cdot \left[ \left( V_{GS,p} - V_{T,p} \right) \right]$$

- Again, the PMOS current can be rewritten as:

$$\boldsymbol{I}_{\scriptscriptstyle DS,n} = \boldsymbol{I}_{\scriptscriptstyle SD,p} = -\boldsymbol{I}_{\scriptscriptstyle DS,p}$$

- we know that for M4:

$$\begin{split} V_{GS,p|M4} &= V_{th} - (V_{DD} - V_{SD3}) \\ V_{DS,p|M4} &= V_{th} - (V_{DD} - V_{SD3}) \end{split}$$

$$I_{SD,4|sast} = -I_{DS,4|sast} = -\frac{1}{2} \cdot k_p \cdot (V_{sh} - V_{DD} + V_{SD3} - V_{T,p})^2$$

$$I_{SD,4|sast} = -\frac{1}{2} \cdot k_p \cdot (V_{sh} - V_{sh} - V_{sh})^2$$

EELE 414 - Introduction to VLSI Design

## CMOS 2-Input NOR Gate - Now we can relate the drain currents knowing that $|_{\Omega_0} = |_{\Omega_A} = |_{\Omega_D}$ giving a a $2^{nd}$ equation relating $V_n$ to $|_{\Omega_D} = |_{\Omega_D} = |_$

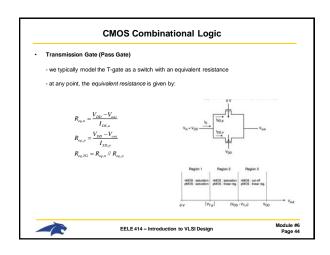

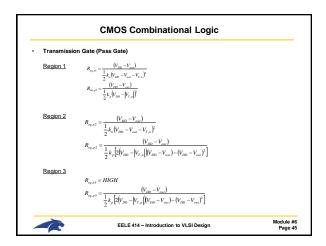

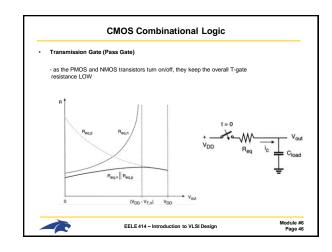

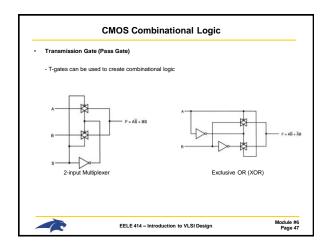

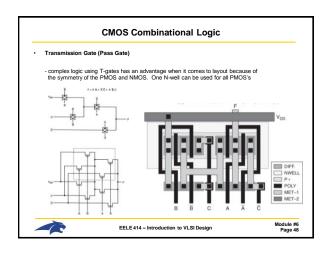

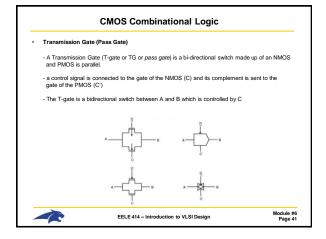

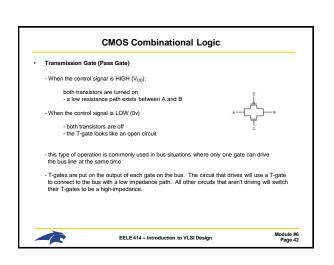

# CMOS Combinational Logic Transmission Gate (Pass Gate) When the T-gate is on, the regions of operation of the transistors will depend on V<sub>in</sub> and V<sub>out</sub> let's say we drive V<sub>in</sub>=V<sub>DD</sub> and initially V<sub>out</sub>=DV As V<sub>out</sub> moves from 0v to V<sub>DD</sub>, the regions of operation for the transistors are as follows: | V<sub>in</sub> = V<sub>DD</sub> | V<sub>DD</sub> |