EELE461/561 - Digital System Design

(Spring 2012)

Course Description

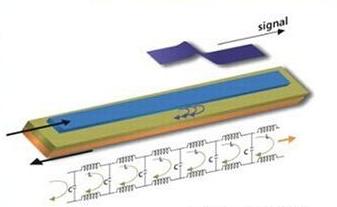

This course introduces students to the physical phenomena that lead to signal degradation when generating and transmitting digital signals. The broadband response of transmission lines will be presented in addition to lumped versus distributed analysis. Emphasis is placed on the physical structures that are used to construct modern digital systems (on-chip Rx/Tx circuitry, on-chip interconnect, IC packaging, PCB's, connectors, and cables). The fabrication process for each component of the digital system will be presented in addition to the tradeoffs between mechanical reliability, cost, and electrical performance. Modern analysis tools will be used to explore these topics including SPICE circuit simulators, EM field solvers, and PCB design/layout software. Modern test equipment will also be presented including Time Domain Reflectrometry (TDR), Vector Network Analysis (VNA), and Jitter Characterization using Real-Time Digital Oscilloscopes. (Syllabus)

Students taking this course will be given the oppertunity to design and fabricate a real printed circuit board through Sunstone Circuits Inc.

Sunstone Circuits: Printed Circuit Boards

Textbook

"Signal and Power Integrity - Simplified" (Required)

Eric Bogatin

Prentice Hall PTR, 2nd Edition, 2009

Time & Location

Lecture (01): EPS 110, MWF, 9:00am-9:50am

Pre-Requisites

EELE 308 - Signals

EELE 334 - Electromagnetic Theory

EELE 371 - Intro to Microprocessor HW/SW

Weekly Schedule

| Day | Date | Topic | Read | Assignments |

|---|---|---|---|---|

| W | 1/11 | M1: Digital Signaling | 1.1-1.6 | - |

| F | 1/13 | M1: Signal Composition (trise·BW) | 2.10 | - |

| M | 1/16 | NO CLASS - MLK Day | - | - |

| W | 1/18 | M1: Signal Composition (Fourier) | 2.1-2.9 | HW 1 |

| F | 1/20 | M1: Signal Composition (BW vs. DR) | 2.11-2.17 | due 1/27 |

| M | 1/23 | M2: Lumped Interconnect Modeling (RLC) | 3.1-3.7 | - |

| W | 1/25 | M3: Distributed Interconnect Modeling (T-line) | 7.4-7.5 | HW 2 |

| F | 1/27 | Lab: Mentor DxDesigner (SPICE, TRAN) | - | due 2/3 |

| M | 1/30 | M3: T-Lines (TD, Z0) | 7.10-7.15 | - |

| W | 2/1 | M3: T-Lines (Γ) | 8.1-8.2 | HW 3 |

| F | 2/3 | Lab: Mentor DxDesigner (SPICE, AC) | - | due 2/10 |

| M | 2/6 | Lab: Mentor DxDesigner (SUBCKT) | - | - |

| W | 2/8 | M3: T-Lines (Terminations) | 8.9-8.10 | HW 4 |

| F | 2/10 | M3: T-Lines (Terminations, Bounce Diagrams) | 8.13-8.19 | due 2/17 |

| M | 2/13 | M3: T-Lines (Γ of LC's) | - | - |

| W | 2/15 | M4: Interconnect Fab (PCBs) | - | HW 5 |

| F | 2/17 | Lab: Mentor DxDesigner/Parts | - | due 2/24 |

| M | 2/20 | NO CLASS - President's Day | - | - |

| W | 2/22 | Lab: Mentor DxDesigner/Parts | - | HW 6 |

| F | 2/24 | M4: Interconnect Fab (PCBs) | - | due 3/2 |

| M | 2/27 | Lab: Mentor PADS Layout | - | - |

| W | 2/29 | Lab: Mentor PADS Layout | - | HW 7 |

| F | 3/2 | Exam #1 | - | due 3/9 |

| M | 3/5 | Lab: Projects | - | - |

| W | 3/7 | Lab: Projects | - | - |

| F | 3/9 | Lab: Projects | - | - |

| M | 3/12 | NO CLASS - Spring Break | - | - |

| W | 3/14 | NO CLASS - Spring Break | - | - |

| F | 3/16 | NO CLASS - Spring Break | - | - |

| M | 3/19 | M5: X-talk (NEXT) | 10.1-10.11 | - |

| W | 3/21 | M5: X-talk (FEXT) | 10.12 | - |

| F | 3/23 | M5: X-talk (SSN) | 10.18 | - |

| M | 3/26 | Lab: Project PCBs | - | - |

| W | 3/28 | Lab: Project PCBs | - | HW 8 |

| F | 3/30 | Lab: Project PCBs | - | due 4/4 |

| M | 4/2 | M6: Diff Signals (Definitions, Structures) | 11.1-11.6 | - |

| W | 4/4 | M6: Diff Signals (Zdiff, Zcomm) | 11.7-11.10 | HW 9 |

| F | 4/6 | NO CLASS - University Day | - | due 4/13 |

| M | 4/9 | M6: Diff Signals (Zodd, Zeven) | 11.14 | - |

| W | 4/11 | M7: Lossy Lines | 9.1-9.5 | HW 10 |

| F | 4/13 | M7: Lossy Lines | 9.6-9.11 | due 4/20 |

| M | 4/16 | Lab: ADS | - | - |

| W | 4/18 | Lab: ADS | - | - |

| F | 4/20 | Exam #2 | - | - |

| M | 4/23 | Lab: TDR & Modeling | - | - |

| W | 4/25 | Lab: TDR & Modeling | - | - |

| F | 4/27 | Lab: TDR & Modeling | - | - |

| T | 5/1 | Projects due, Tuesday @ 6pm | - | - |

Homework Information

Homework 1 - Risetime BW Product

Handout (PDF)

Paper (561 only) (PDF)

Homework 2 - Interconnect Modeling

Handout (PDF)

Homework 3 - RMS Risetime, T-Lines and SPICE

Handout (PDF)

Homework 4 - T-Line Reflections and SPICE

Handout (PDF)

Homework 5 - T-Line Terminations

Handout (PDF)

Homework 6 - P CB Impedances

Handout (PDF)

Homework 7 - PCB Fab Drawings

Handout (PDF)

Homework 8 - Signal Cross-Talk (NEXT & FEXT)

Handout(PDF)

Homework 9 - Return Cross-Talk (SSN)

Handout (PDF)

Homework 10 - Lossy Lines (SSN)

Handout (PDF)

Lecture Notes

- Module 1: Signal Composition (PPTX) (PDF)

- Module 2: Lumped Interconnect Modeling (PPTX) (PDF)

- Module 3: Distributed Interconnect Modeling (PPTX) (PDF)

- Module 4: Interconnect Fabrication (PCBs) (PPTX) (PDF)

- Module 5: Cross-Talk (PPTX) (PDF)

- Module 6: Differential Signaling (PPTX) (PDF)

- Module 7: Lossy Lines (PPTX) (PDF)

Final Project

Handouts

Course Documents

PCB Design Information

NOTE: At minute 11 of this video, I tell you to delete the local part library (.library)

when setting up a project in DxDesigner. DO NOT DO THIS. The newer versions of DxDesigner

need the local part library and will not forward to layout without it. If you delete

it and try to forward to layout, you will get a very unhelpful error message.

- Mentor PADS 2009.1 Video Tutorial - Creating a Board Outline - 15min (HTML)(WMV)

- Mentor PADS 2009.1 Video Tutorial - Creating Library Parts - 37min (HTML)(WMV)

- Mentor PADS 2009.1 Video Tutorial - Creating a Fab/Drill Drawing - 22min (HTML)(WMV)

- Mentor PADS 2009.1 Video Tutorial - Routing & Planes - 26min (HTML)(WMV)

- MSU PADS 2007 Tutorial (1.5M)

- Example Fab/Drill Drawing (73k)

- MSU Bobcat Logo in PADS (1.3M)

- MSU Logo in PADS (1.7M)

- Mentor PADS 2009.1 Software (1G)

- Mentor PADS 2009.1 Patch (45k)

- Replace the "netlist.prp" file in:

- C:\MentorGraphics_PADS2009.1\9.1PADS\SDD_HOME\standard\ with this one.

Simulation Information

- Mentor PADS 2009.1: DxDesigner & HyperLynx Analog (650k)

- MSU Advanced Design System (ADS) Tutorial (195k)

- MSU Advanced Design System (ADS) Eye Diagrams (PPT, 800k)

- MSU Advanced Design System (ADS) Momentum (PPT 650k)

- Guide to Importing TDR Data into ADS (DOC 30k)

- TIM Conversion Spreadsheet (XLS 800k)

- Tektronix TDR Source Measurement in CSV format (CSV, 20k)

- Tektronix TDR Source Measurement in TIM format (TIM, 150k)

TDR/TDT Information

- Theory of Time Domain Reflectrometry, from Agilent (200k)

- Measuring Lumped C & L Using TDR, from Agilent (511k)

- Signal Integrity Analysis Using TDR/TDT, from Agilent (5.3M)

- Measuring Cross-Talk using TDR (624k)

Project Information

- Project Description (PDF)

- IEEE Journal Template (DOC 100k)

- Example IEEE Formatted Paper (DOCX 10M)

- Example IEEE Formatted Paper (PDF 2M)

- Edge Mount SMA Connector Datasheet (172k)