# **Electrical Engineering 234**

Electrical Engineering Circuit Laboratory

by Robert C. Maher, Assistant Professor with Duane T. Hickenbottom, Graduate Assistant

> University of Nebraska Lincoln Department of Electrical Engineering

#### Contents

- Laboratory Procedures and Information

- Lab #1: Response of RLC Circuits

- Lab #2: Impedance I: Phasor Relationships for Simple Circuits

- Lab #3: Impedance II: Input Impedance and Active Circuits

- Lab #4: Terminal Characteristics of Semiconductor Diodes

- Lab #5: Nonlinear Circuit Applications: Diodes and Op Amps

- Lab #6: Bipolar Junction Transistors

- Lab #7: Electrical Resonance and Resonant Circuits

- Lab #8: Metal-Oxide-Semiconductor Field-Effect Transistors

- Lab #9: Frequency Response and Filters

- Lab #10: Power Relationships and Power Factor

- Lab #11: *Transformers*

- Lab #12: Two-Port Parameters

- Appendix: Resistor Color Bands

This manual and the experiments were compiled, written and/or edited by Robert C. Maher, Assistant Professor, with graduate assistant Duane T. Hickenbottom during Spring Semester 1992.

# Laboratory Procedures and Reports

The purposes of this laboratory course are to practice essential laboratory measurement and report preparation skills, to reinforce the concepts and circuit analysis techniques taught in EEngr 214 and EEngr 260, and to gain an increased understanding of some of the practical issues of electrical engineering circuit analysis and design.

#### Lab Manual Format

Each of the entries in this lab manual consists of several sections: Abstract, Introduction and Theory, References, Pre-lab Preparation, Experiment, and Results.

The *Abstract* is a brief summary describing the experiment.

The *Introduction* and *References* sections provide some of the background information necessary for the experiment. This material is intended only to be supplementary to the classroom lectures and exercises in EEngr 214 and 260.

The *Equipment* section lists the major components and measurement instruments needed to perform the experiment.

The *Pre-lab Preparation* section contains several tasks that must be performed *BEFORE* arriving at the lab. The pre-lab typically requires calculation of specific component values, prediction of the behavior to be measured in the lab, and preparation using computer simulation.

The *Experiment* section contains a description of the circuits, components, and the actual lab measurements to be recorded in the lab notebook. This section is the *minimum* required effort: you are encouraged to try additional ideas once the required measurements are made. Ask the lab teaching assistant (TA) for guidance with this.

Finally, the *Results* section lists the **minimum** required items to be presented in the final lab report.

Your grade in this laboratory course is based upon several components.

| Pre-lab exercises                              | 20% |

|------------------------------------------------|-----|

| TA evaluation of your lab skills and knowledge | 20% |

| Lab practical final exam                       | 20% |

| Lab results and reports                        | 40% |

The *pre-lab exercises* are to be turned in at the beginning of the lab period. If you need any of the pre-lab results in order to perform the experiment you will have to make a copy of your pre-lab solutions, preferably in your lab notebook. Your TA should grade the pre-labs during the lab period and return them to you before you leave.

The *TA evaluation of lab skills* will be based on how well you respond to the questions he or she will ask you during the experiments throughout the semester. In other words, the TA will occasionally ask questions to ascertain whether you (i) understand the theory and rationale for the experiment, (ii) are able to operate the lab instruments properly, and (iii) can express your knowledge in a meaningful, concise manner. *Hint:* if you do not understand the lab concepts it is probably advisable to ask your TA for help *before* he or she puts you on the spot!

A *lab practical exam* will be given in order for you to demonstrate your analytical ability and proficiency with the equipment, circuits, and concepts considered in this course. The content, format and schedule of the practical exam will be determined by your TA.

Finally, the largest individual component of your lab grade will be based on your *lab results and reports*. Some suggestions for your lab notebook and lab reports are given next.

# Lab Notebook

Good laboratory practice begins with pre-lab preparation. It is essential to read the lab manual, perform the pre-lab assignments, and carefully think through all the steps to be performed and the measurements to be made. This process centers around the need for good documentation: a lab notebook.

The lab notebook is a complete record of ALL work pertaining to the experiment. It is not necessary to include lengthy explanations and procedures in the notebook, but *the*

*entries must be sufficient for another person to understand your methods and replicate the experiment.* The purpose of the notebook is to follow the required practices of industrial or academic research and development laboratories, where complete and accurate records of laboratory work are vital. The lab notebook is a legally recognized paper that is essential in documenting inventions, discoveries, and patent disclosures. Some companies require lab notebooks to be officially notarized and filed so that any legal questions later on can refer directly to the original, unaltered notebook entries. Although a notary seal is not required for your lab notebooks in this course, be sure to keep the importance of good experimental note taking in mind.

The pages of the notebook must be bound (not loose leaf or spiral) and should be numbered consecutively. The notebook entries must be in ink, and no pages should be left blank between entries. Begin the entries for each experiment on a new page, giving the title of the experiment, your name, the name of your lab partner, and the date. In case some of the data or calculations written in the notebook turn out to be in error, *do not* tear out the page or completely obliterate the entries: a *single line* through the error is preferred. This way there is no question regarding the legitimacy and completeness of the notebook material. *Furthermore, you will <u>not</u> be penalized in this course for having lined-out errors and corrections in your notebook.*

Pre-lab preparation results can be written in the notebook, along with an outline of the experiment to be performed, circuit sketches, and anticipated results. The expectations and predictions from the pre-lab work are extremely important in guiding the measurements actually made in the lab. For example, if we expect a linear relationship  $(y = m^*x)$  between two circuit parameters and measure something completely different, we are in a position to double-check the circuit and the measurement techniques to discover whether the discrepancy is due to an incorrect circuit, limitations of the measurements, or faulty assumptions and predictions. Similarly, the ideal number and spacing of data points on a graph can guide the number and spacing of lab measurements. Always determine the level of accuracy of each measurement and include these limitations with the results.

The process of comparing expectations and results is best accomplished *during* the lab period: this way any questionable data can be verified and further measurements can be made. Along with tables of the measured data it is useful to sketch graphs of the measurements. This helps to spot trends or errors in the data. For the same reason it is also desirable at least to "work through" the required solutions to the Results section of the experiment *before* leaving the lab.

<u>All jobs in electrical engineering require proficiency in technical writing</u>. The written lab report is just one example. The report should be written specifically to meet the needs of the reader, meaning that the writing must be brief, interesting, and complete. It is good engineering practice when writing to always begin with a *summary* of each important conclusion, followed by the *results and reasoning* that led to that conclusion, and finally a *review* of what was stated. Keep in mind that the specific format and content requirements of the lab report may vary depending upon the preferences of the reader, in this case the lab TA.

In addition to the technical content of your report, you will also be graded on your use of the English language. Be certain that your spelling, punctuation, and grammar are correct.

The report should be assembled in some reasonable manner, such as:

• <u>Cover Page</u> showing the experiment title and number, date experiment was performed, date report was finished, and the name of the author and partner.

• <u>Abstract</u> giving a summary of the *complete* report. The abstract is normally written last, and should ordinarily be no more than 3 or 4 sentences.

• <u>Introduction</u> giving a 1 or 2 paragraph explanation of what the reader must know to understand the report. Basically, the introduction indicates whether *you* understood what the lab was all about!

• <u>Procedure</u> describing the steps used in the lab. This need only be sufficient to recreate the experiment in conjunction with the lab notebook, *not* a lengthy minute-by-minute account.

• <u>Results and Discussion</u> of the experiment, including the requested information from the lab manual, comparisons with pre-lab predictions, and *reasonable* explanations of any difficulties or surprising results. Tables of "raw" data should be left in the notebook, not in the report, except where necessary to support the discussion. *Do* include graphs of the results where appropriate. Include a discussion of the methods and circuits used in the experiment and indicate any extra measurements or investigations you made in addition to the steps in the lab manual. Indicate important observations *you* were able to make that other students might have missed.

• <u>Conclusion</u> giving the main items learned in the experiment.

Before finalizing the report to turn in, look over the entire report with a critical eye. Is the report complete and concise? Is the substance of the report good enough *that you would show it to a potential employer* as an example of the quality of work you do? Does it indicate that you know what you are doing? Are the sections labeled? Are the graphs labeled and *interpreted* (slopes, breakpoints, etc. identified)? Are the circuit diagrams accurate and labeled? Do you tend to use imprecise phrases and meaningless platitudes like "very large", "negligible", "this experiment demonstrates to the student...", "the results validate the theory", "the measurements are cruddy because ideal conditions do not exist", etc.?

#### Lab Safety

A few simple electrical laboratory safety guidelines apply:

- 1) There must always be at least three people in the lab at one time: one able to assist an injured person and one to go for help.

- 2) All electrical apparatus that connects to the AC power line must have a protective ground through a three-wire power cable, or be of approved double-insulated construction.

- 3) Always check and re-check circuit wiring before applying power. Always have a single switch or button that will immediately remove power from the circuit in case of trouble.

- 4) Always switch the circuit power off before changing components or connections. *It is tempting to become lazy and change connections in low-power circuits with the supply on, but this is asking for trouble in the form of unintentional short circuits and blown components, or serious damage and injury in the case of high power circuits.*

- 5) Always ask for directions or help if you are unsure of the correct measurement procedure or circuit connection. *Be honest with yourself*: if you don't understand what you are doing, seek assistance from the lab TA.

Some Final Words...

This lab course has been put together to benefit a specific customer: *you*. If you are having difficulty understanding the experiments and concepts because of the way in which the material is presented, let your lab TA know! You will notice that part of the results section for each experiment is a question asking how you would change the experiment to make it more understandable, more interesting, and more useful to you.

This lab course covers a wide range of topics. A few of the topics you will probably find easy to master, while most topics will seem complicated and perhaps even incomprehensible. *Do not expect simply to walk into the lab without preparation and get the experiment accomplished!* You will need to allow sufficient time *before* the lab period to look over the experiment, understand the concepts and procedures, and prepare the pre-lab assignments. A few extra minutes in preparation will make your experience in the lab much more enjoyable and meaningful. Getting into the habit right away of setting aside a specific period of time each week for lab preparation will be much easier than always trying to squeak it in the night before the experiment is to be done.

In writing a lab manual it is difficult to avoid the need for a certain amount of cookbook directions: "assemble the circuit of Figure x, connect wire A to point B, write down the voltage at point C, repeat until done". Unfortunately, it is possible that some of you may begin to feel that good engineering laboratory practice consists entirely of following tedious directions. I have found many students and even working engineers who are extremely queasy about having to analyze the cause of a malfunctioning device or having to design or modify an electronic system to meet a specific requirement. The whole process of engineering can seem overwhelming when you are out on the job and no "cookbook" is available for every project.

As you work on the experiments in this course, keep in mind that electrical engineering involves a generous mix of *theory, analytical skills, creativity, and practical experience*. Theory and analytical skills are what you are taught in the classroom. Creativity involves a good understanding of the strengths and limitations of electrical engineering components, concepts, and technology. But of all the design ingredients, *practical experience* is perhaps the most important element. This course and your other lab courses are intended to help you gain some of this practical experience. Take this opportunity to try out your own ideas. Ask questions of your TAs, professors, electronics technicians, and even other students. Learn from your own mistakes--and learn from the mistakes of others! Besides, this lab should also be fun!

Revised 7/94

#### Resistors (5% tolerance, carbon or carbon film, 1/4 watt)

| 1/4 watt)                                 |               |  |  |  |

|-------------------------------------------|---------------|--|--|--|

| Qty                                       | Nominal Value |  |  |  |

| 2                                         | 100 <b>Ω</b>  |  |  |  |

| 2<br>2                                    | 220Ω          |  |  |  |

| 1                                         | 300Ω          |  |  |  |

| 2<br>1                                    | 680Ω          |  |  |  |

| 1                                         | 750Ω          |  |  |  |

| 4                                         | 1k <b>Ω</b>   |  |  |  |

| 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | 2.2kΩ         |  |  |  |

| 2                                         | 5.6kΩ         |  |  |  |

| 2                                         | 6.8kΩ         |  |  |  |

| 2                                         | 10k <b>Ω</b>  |  |  |  |

| 2                                         | 12k <b>Ω</b>  |  |  |  |

| 2                                         | 22kΩ          |  |  |  |

|                                           | 33k <b>Ω</b>  |  |  |  |

| 1                                         | 47kΩ          |  |  |  |

| 1                                         | 68kΩ          |  |  |  |

| 2                                         | 100k <b>Ω</b> |  |  |  |

| 2                                         | 220kΩ         |  |  |  |

| 2<br>2<br>2<br>2<br>2                     | 430kΩ         |  |  |  |

| 2                                         | 470kΩ         |  |  |  |

| 2                                         | 1ΜΩ           |  |  |  |

|                                           |               |  |  |  |

# Semiconductors

| Qty | Component                            |

|-----|--------------------------------------|

| 1   | Type 741 Op amp                      |

| 1   | Type BS170 NMOS Enhancement FET (not |

|     | BS170P !)                            |

| 2   | Type 2N2222 NPN BJT                  |

| 4   | Type 1N4001 Silicon Diode            |

# Capacitors

| Qty | Nominal Value and Type                   |  |  |

|-----|------------------------------------------|--|--|

| 2   | 0.001µF (100 volts, polyester or plastic |  |  |

|     | film, ±10% tolerance or better)          |  |  |

| 2   | 0.0022µF "                               |  |  |

| 2   | 0.01µF "                                 |  |  |

| 2   | 0.022µF "                                |  |  |

| 2   | 0.047µF "                                |  |  |

| 2   | 0.1µF "                                  |  |  |

| 2   | 0.22µF "                                 |  |  |

| 2   | $10\mu F$ (35 volts or more, aluminum    |  |  |

|     | electrolytic, ±20% tolerance or better)  |  |  |

| 4   | 22µF "                                   |  |  |

| Lab # 1 |                          |

|---------|--------------------------|

| TITLE:  | Response of RLC Circuits |

#### ABSTRACT

This experiment considers the response of simple series RLC circuits. It should be noted the solutions for parallel RLC circuits are duals of the solutions for series RLC (replace **R** with **1/R**, **L** with **C**, **i** with **v**) As with RC and RL circuits, the output of any RLC circuit can be analyzed to determine the total response, consisting of both the steady-state (forced) response and the transient (natural or complementary) response, for any given input. Our analysis will cover only constant (DC) forcing functions as inputs. This lab includes SPICE analysis and construction of simple **series** RLC circuits.

#### INTRODUCTION AND THEORY

Linear second order systems are common to many fields of study. Mechanical engineers use the same equations to solve for the displacement of a spring-supported mass subjected to viscous damping and physicists solve for the motion of a simple pendulum. While electrical engineers usually solve for the current or voltage in a circuit, mechanical engineers may solve for displacement or motion of a mass. No matter what physical components are used (inductors or springs, capacitors or masses, resistors or dashpots) or the response desired (current or force, voltage or velocity), the same form of solutions will be obtained (damped, overdamped, or critically damped). The same equations are also very important in control systems analysis (EEngr 444).

Many circuits used in communications networks can be modeled well by combining ideal resistors, capacitors, and inductors. RLC circuits are an important part of some of the electronic amplifiers found in every radio receiver and allow the amplifiers to produce a large voltage amplification over a narrow band of signal frequencies and nearly zero amplification outside this band. Parallel RLC circuits are also used in multiplexing filters and harmonic suppression filters.

Previous experiments with RL and RC circuits involved only one storage device and were solved with a first order differential equation. Circuits involving both inductors and capacitors require solving a 2nd order differential equation.

$$\frac{\mathrm{d}^2 \mathrm{i}}{\mathrm{d}t^2} + \frac{\mathrm{R}}{\mathrm{L}}\frac{\mathrm{d}\mathrm{i}}{\mathrm{d}t} + \frac{\mathrm{i}}{\mathrm{LC}} = 0,$$

or

$$s^2 + 2\alpha s + \omega_o I = 0.$$

For the second form,  $\alpha$  (exponential *damping coefficient*)=**R/2L** and  $\omega_0$  (resonant frequency) =  $(LC)^{-\frac{1}{2}}$ . Often  $\omega_0$  is normalized to 1 by substituting  $\zeta$  (damping ratio)= $\alpha/\omega_0$ . Another important substitution (for the underdamped solution) is  $\omega_n$ (natural or damped frequency)=  $\sqrt{(\omega_0^2 - \alpha^2)}$  The 3 most important forms of the solution for i are:

| Case I: $\alpha > \omega_0$ | >0                      | $(\zeta > 1)$ The overdam | ped case.                    |

|-----------------------------|-------------------------|---------------------------|------------------------------|

| Case II:                    | $\alpha < \omega_0$     | $(0 < \zeta < 1)$         | The <i>underdamped</i> case. |

| Case III:                   | <b>α=ω</b> <sub>0</sub> | $(\zeta = 1)$ The $c$     | ritically damped case        |

See the Irwin text for a comparison of the 3 cases. Notice the underdamped response reaches steady state fastest but overshoots. Overdamped does not overshoot but takes longer to reach steady state than the critically damped response. Critically damped reaches steady state as fast as possible **without** overshooting.

#### REFERENCES

See chapter 8 of the text by J. David Irwin, *Basic Engineering Circuit Analysis*, 4th ed., Macmillan Publishing Co., 1993.

For help with PSPICE (esp. .STEP and .MODEL statements) see paperback by P. W. Tuinenga, *SPICE: A Guide to Circuit Simulation & Analysis Using PSpice*®, 2nd edition, Prentice Hall, 1992.

For electrical/mechanical equivalents, see section 2.7, by J.J. D'Azzo and C.H. Houpis, *Linear Control System Analysis and Design*, 2nd ed., McGraw-Hill Book Co, 1981, or the current EE 444 (Control Systems) textbook.

#### EQUIPMENT

Oscilloscope Signal generator Variable inductor (0.01 to 0.1 H by .01 H) Assorted resistors and clips Inductance/capacitance meter 0.1  $\mu$ F capacitor Potentiometer (0-1k $\Omega$ ) Ohmmeter

PRE-LAB PREPARATION

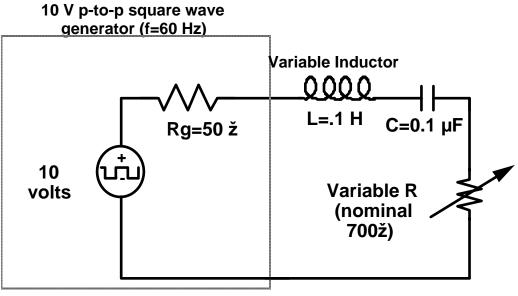

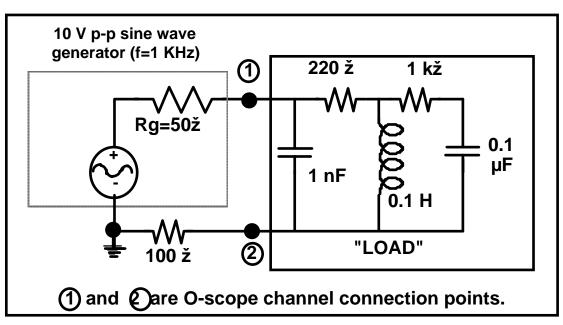

(I) Refer to Figure 1.1. For the pre-lab the voltage source is a 10 V power supply (with an internal impedance of 50  $\Omega$ ) which is switched on at time t=0.

- (a) Solve for i (current) through the potentiometer.

- (b) What are  $\alpha$  (damping coefficient),  $\zeta$  (damping ratio),  $\omega_0$  (resonant frequency), and  $\omega_n$  (natural frequency)?

- (c) Is the circuit over, under or critically damped? Why?

(II) Solve for  $V_C(t)$ , the capacitor voltage.

Figure 1.1

(III) Using the circuit of part (I), what value of resistance (R) will provide critical damping? What are  $\alpha$  and  $\omega_0$ ?

(IV) Do a PSpice transient analysis using initial values from (I). Vary the **resistance** to get three plots showing under, over, and critical damping. Use PROBE to plot (a) the three currents and (b)  $V_C(t)$ , the three capacitor voltages, on two separate curves. **NOTE:** First replace the 10 V step input with a 10 V peak-peak square wave which has a period long enough to show the underdamped response. (A square wave generator will be used in the lab to produce a periodic signal which can be viewed on the oscilloscope.) The three voltage or current curves may be plotted on the same curve either by creating three separate circuits driven by the same source, OR by using the .STEP statement. *For example*, a "stepped" resistor could be implemented using:

```

RSTEP 1 2 POTMOD 50K

.MODEL POTMOD RES

.STEP RES POTMOD(R) 0.95 1.05 0.05

```

On the first line of this example a resistor arbitrarily named RSTEP has a nominal value of 50K ohms and is connected between nodes 1 and 2 in the circuit. The resistor is described by a model arbitrarily named POTMOD. The second line is the model description for POTMOD, and states simply that this model is a resistor model (type RES). The last line of the example is the .STEP command which causes the entire PSpice analysis to be run for RSTEP=47.5K, 50K, and 52.5K, corresponding to the 50K nominal value and multipliers from 0.95 to 1.05 in 0.05 steps.

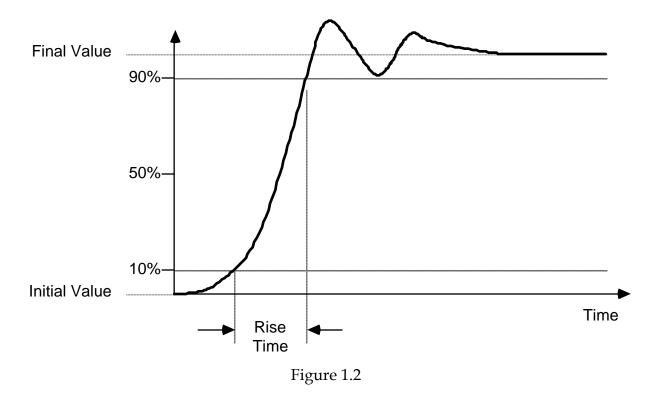

Measure the *overshoot* (%) and the *rise time*  $(t_r)$  where

Overshoot (%) =

$$\left(\frac{y(t)_{\text{maximum}} - y(\infty)}{y(\infty)}\right) \times 100\%$$

Rise time  $(t_r) = time[0.9 \cdot y(\infty)] - time[0.1 \cdot y(\infty)]$

Rise time is defined as the time required for the response to move from 10% to 90% of the steady state value because it is difficult to measure exactly when the response reaches its final value. An example of rise time is shown in Figure 1.2.

#### EXPERIMENT

(1) Use the inductance/capacitance meter to measure the inductance of the variable inductor for each setting. Use an ohmmeter to measure the internal resistance for each setting.

(2) Use the same meter to measure the capacitance and ESR (equivalent series resistance) of the capacitor.

(3) Connect the circuit as in Figure 1.1 but substitute a signal generator set to 10V (peak-peak) square wave for the 10V step input. Use a combination of resistors and a potentiometer to obtain the 3 values of resistance from prelab IV. NOTE: Use resistors from lab kit if you need to obtain resistance >1k $\Omega$ .

Measure and graph i(t) and  $v_c(t)$  for all 3 values of the resistance (from prelab IV).

Now adjust the potentiometer/resistors until critical damping is achieved (just before curve begins to overshoot). Measure the **actual** resistance needed to obtain critical damping.

(4) Adjust the resistance to the value (from prelab IV) which causes the circuit to be underdamped. By measuring the time period for one oscillation of the "ringing", determine  $\omega_n$  (natural frequency).

#### RESULTS

(a) List the actual values of the inductor for each setting. Which setting had the largest % error? What was the % error in the capacitor value?

(b) Compare the SPICE i(t) and  $v_c(t)$  curves to the lab experimental curves, especially the critically damped curve. Discuss the % overshoot, rise time, and the exact value of resistance for critical damping. What were the % differences and why?

(c) Using the value of  $\omega_n$  determined experimentally (part 4), calculate the total resistance in this RLC circuit and compare to the value of R used in part 4. Discuss any differences.

(d) When viewing the square wave output of the signal generator (while connected to the RLC circuit), why is the square wave slightly distorted?

(e) Does the signal generator impedance affect the circuit performance? When might the generator impedance need to be taken into account? Does the internal resistances of the inductor, capacitor, and signal generator affect the response?

(f) Is there any part of this lab which you do not understand? What can be done to improve this experiment?

Revised 7/94

## Lab # 2 TITLE: Impedance I: Phasor Relationships for Simple Circuits

#### ABSTRACT

The response of an electrical network to a sinusoidal input forcing function is an extremely important characteristic in electrical engineering. This laboratory exercise investigates the amplitude and phase relationships between voltages and currents in electrical networks driven by sinusoidal sources. In particular, the concepts of *phasors* and *impedance* are examined.

#### INTRODUCTION AND THEORY

One of the first concepts considered in electrical engineering is the relationship between voltage and current in a resistor: v=iR (Ohm's Law). As we will see in this lab, it is also possible and useful to generalize Ohm's Law to represent arbitrary combinations of resistors, capacitors, and inductors, using the concepts of *phasors* and *impedance*. First, a description of the behavior of the basic circuit elements to sinusoidal input functions is considered.

#### Voltage and Current in R, L, and C

The meaning of Ohm's Law for resistors is unchanged if the voltage, V, and current, I, are allowed to be time-varying<sup>\*</sup>. For example, if

then

$$v(t) = A \cdot cos(\omega t + \phi),$$

A

$i(t) = R \cos(\omega t + \phi),$

where Ris the resistance in ohms,

- A is the amplitude of the time-varying voltage (volts),

- $\omega$  is the angular frequency of the signal (radians/sec),

- t is time (seconds), and

- $\phi$  is an arbitrary phase offset (radians).

<sup>\*</sup> Note that although cosine "driving" functions are used here, sine functions apply just as well.

The important feature of this result is that the voltage and current are *in phase*, because the two waveforms have the same time dependence,  $\cos(\omega t + \phi)$ . It is true in general that the voltage and current in a resistor are *in phase*.

Now consider the relationship between current and voltage in an inductor: v = L di/dt. For example, letting the current be time varying,

$\begin{aligned} i(t) &= B \cdot \cos(\omega t + \phi), \\ then \qquad v(t) &= -\omega \cdot L \cdot B \cdot \sin(\omega t + \phi). \end{aligned}$

Using the relationships  $\sin(\theta) = \cos(\theta - \pi/2)$ , and  $-\cos(\theta) = \cos(\theta + \pi)$ , the expression for v(t) can be rewritten

$$v(t) = \omega \cdot L \cdot B \cos(\omega t + \phi + \pi/2).$$

Note that unlike the resistor, the voltage and current for an inductor are *not* in phase. The total instantaneous phase of the voltage, ( $\omega t + \phi + \pi/2$ ), is always  $\pi/2$  (one quarter cycle) greater than the phase of the current, ( $\omega t + \phi$ ). Thus, the *voltage leads the current* by  $\pi/2$  in an inductor. In other words, the maxima, minima, zero-crossings, etc. of the voltage occur one quarter of a cycle before the corresponding extrema of the current.

A similar examination of the voltage and current relationship for a capacitor (i = C dv/dt) reveals that the *current leads the voltage* by  $\pi/2$ , i.e.,

then

$$\begin{aligned} \mathbf{v}(t) &= \mathbf{A} \cdot \cos(\omega t + \phi), \\ \mathbf{i}(t) &= -\omega \cdot \mathbf{C} \cdot \mathbf{A} \cdot \sin(\omega t + \phi) = \omega \cdot \mathbf{C} \cdot \mathbf{A} \cdot \cos(\omega t + \phi + \pi/2). \end{aligned}$$

Phasors

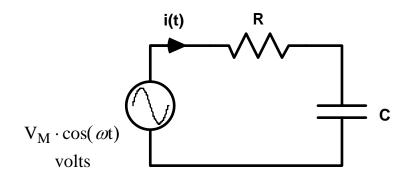

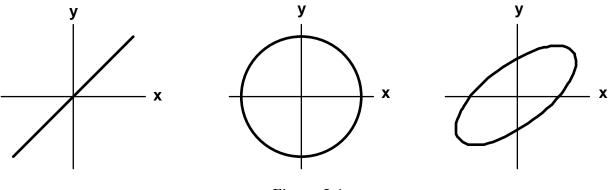

Although the voltage and current analysis of the basic circuit elements is relatively simple using trigonometric identities, the analysis situation becomes more difficult for networks involving combinations of the various elements. Consider for example the "simple" network shown in Figure 2.1.

Figure 2.1

The conventional way to find the loop current i(t) is to solve the differential equation describing the circuit:

$$V_{\rm M} \cdot \cos \omega t = \mathbf{R} \cdot \mathbf{i}(t) + \frac{1}{C} \int \mathbf{i}(t) dt$$

Assuming the current is of the form  $i(t) = \alpha \cos(\omega t + \varphi)$ , we can determine the unknown constants  $\alpha$  and  $\varphi$ , which gives the solution:

$$i(t) = \frac{\omega CV_{M}}{\sqrt{(\omega CR)^{2} + 1}} \cdot \cos\left(\omega t + \tan^{-1}\frac{1}{\omega CR}\right)$$

or

$$= \frac{V_{M}}{\sqrt{R^{2} + (\frac{1}{\omega C})^{2}}} \cdot \cos\left(\omega t + \tan^{-1}\frac{1}{\omega CR}\right)$$

Solving the differential equation directly like this is certainly feasible for simple circuits, but this technique becomes rather unwieldy for circuits with more components, loops, and branches. The main difficulty is in keeping track of the phase relationships between the various nodes in the network. Instead, we will often use an analysis approach which makes use of complex number theory and the *linearity property* of the elementary circuit elements.

The complex number theory of interest here can be summarized by Euler's relationship

$$e^{j\omega t} = \cos \omega t + j\sin \omega t$$

Note that this allows us to convert between cosines and sines and a complex exponential form. The advantage to the complex exponential form is that we merely

need to *add* exponents when we multiply exponentials together. This will come in handy when the relative phase difference between voltage and current in a network is considered.

The concept of linearity that we will need is *superposition*. Recall superposition means that the total response of a circuit due to the sum of two or more inputs is simply the sum of the responses due to each input if acting alone. For our purposes here, *the usefulness of the linearity property is that we are free to introduce a complex exponential whenever it makes the mathematical analysis easier, as long as we remember to take the "real part" when we get to the solution.* In short, the imaginary part of the complex exponential simply "goes along for the ride" to assist with the mathematical analysis.

The other important result of linearity is that if the circuit is driven by a single sinusoidal (sine or cosine) source, *all the voltages and currents in the network will also be sinusoidal but with possibly different amplitudes and phases relative to the source*. In other words, each term in our network equations will contain the complex exponential factor  $e^{j\omega t}$ . This is the heart of steady-state sinusoidal analysis.

We will indicate the amplitude and phase relationship through the use of *complex notation*: a complex number is used to indicate only the *amplitude* and *phase* of voltages and currents in the circuit (since the sinusoidal time variation factor  $e^{j\omega t}$  is common to all terms). For example, a circuit current described by the equation

$$i(t) = I_0 \cos(\omega t + \theta)$$

can be written in complex exponential form (Euler's equation) as

$$\mathbf{i}(\mathbf{t}) = \operatorname{Re}\left\{\mathbf{I}_{0} \mathbf{e}^{\mathbf{j}(\boldsymbol{\omega}\mathbf{t}+\boldsymbol{\theta})}\right\}$$

and in polar complex form as

$$i(t) = \operatorname{Re} \left\{ I_0 \angle \theta \ e^{j\omega t} \right\}.$$

Finally, we can simplify the notation by dropping the *implied*  $e^{j\omega t}$  term and the Re{} operator, leaving the *phasor notation*:

$$\mathbf{I} = \mathbf{I}_0 \angle \theta = \mathbf{I}_0 e^{j\theta} = \mathbf{I}_0 (\cos \theta + j\sin \theta)$$

where the boldface I reminds us that the *phasor* quantity I is a complex number.

Let's use these ideas to re-analyze the circuit of Figure 2.1. We first replace the voltage source by the complex exponential expression  $V_M e^{j\omega t}$ . Since we know that the resulting current must also be sinusoidal, we can represent the current as the complex exponential  $I_M e^{j(\omega t + \phi)}$ , where  $I_M$  is the unknown amplitude of the current and  $\phi$  is the unknown phase (relative to the phase of the source). The differential equation becomes

$$V_{M}e^{j\omega t} = R \cdot I_{M}e^{j(\omega t + \phi)} + \frac{1}{C}\int I_{M}e^{j(\omega t + \phi)} dt$$

Performing the integral and regrouping,

$$V_{M}e^{j\omega t} = I_{M}e^{j\phi}e^{j\omega t} \cdot \left(R + \frac{1}{j\omega C}\right)$$

Note again that both sides of this equation have an  $e^{j\omega t}$  factor. Rewriting in phasor notation gives

$$\mathbf{V} = \mathbf{I} \cdot \left( \mathbf{R} + \frac{1}{j \omega \mathbf{C}} \right)$$

Now solving for the phasor current,

$$\mathbf{I} = \frac{\mathbf{V}}{\mathbf{R} + \frac{1}{j\omega C}} = \frac{\mathbf{V}_{\mathrm{M}} \angle 0^{\circ}}{\mathbf{R} - j\frac{1}{\omega C}} = \frac{\mathbf{V}_{\mathrm{M}} \angle 0^{\circ}}{\sqrt{\mathbf{R}^{2} + \left(\frac{1}{\omega C}\right)^{2}} \angle -\tan^{-1}\frac{1}{\omega CR}}$$

$$= \frac{\mathbf{V}_{\mathrm{M}}}{\sqrt{\mathbf{R}^{2} + \left(\frac{1}{\omega C}\right)^{2}}} \angle \tan^{-1}\frac{1}{\omega CR}$$

As the final step we convert from phasor notation back to the time-domain current by reintroducing the real part of the time dependence (  $\cos(\omega t)$  ), yielding

$$i(t) = \frac{V_M}{\sqrt{R^2 + (1/\omega C)^2}} \cdot \cos\left(\omega t + \tan^{-1}\frac{1}{\omega CR}\right)$$

which is the same result (*whew*!) as was obtained with the differential equation approach. The important advantage of this approach is that the mathematics involves mostly simple algebraic operations on the magnitudes and phases.

It is important to notice that the use of phasors and complex exponentials is based on the *cosine* function because the cosine is associated with the real part via Euler's equation. To represent a real *sine* function we need to include the 90° phase difference between the cosine and sine functions, i.e.,

but

$\mathbf{K} \cdot \cos(\omega t \pm \theta) \iff \mathbf{K} \angle \pm \theta$

$$\mathbf{K} \cdot \sin(\omega t \pm \theta) \iff \mathbf{K} \angle \pm \theta - 90^\circ$$

#### Impedance

It is interesting to examine these elementary voltage and current results. If we look at the complex ratio of phasor voltage and phasor current for each of the basic circuit elements we find:

Resistor, R:

$$\frac{\mathbf{V}}{\mathbf{I}} = \mathbf{R}$$

Inductor, L:

$$\frac{\mathbf{V}}{\mathbf{I}} = \mathbf{j}\omega\mathbf{L} = \omega\mathbf{L}\angle 90^{\circ}$$

Inductor, L:

$$\frac{\mathbf{V}}{\mathbf{I}} = \frac{1}{\mathbf{j}\omega\mathbf{C}} = -\mathbf{j}\frac{1}{\omega\mathbf{C}} = \frac{1}{\omega\mathbf{C}}\angle -90^{\circ}$$

Capacitor, C:

The V/I complex ratio is called the *impedance*, often denoted by the symbol Z. The units of impedance are ohms, since the ratio of volts to amps is defined to be ohms. The

impedance of a resistor is a purely *real* number with no frequency dependence: the resistance. The impedance of inductors and capacitors, however, is a purely *imaginary* number that *varies with the sinusoidal driving frequency* ( $\omega$ ):  $j\omega L$  and  $1/j\omega C$ , respectively. A circuit containing a combination of resistors, capacitors, and/or inductors will, in general, have a *complex* impedance.

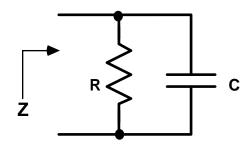

The really useful thing about analyzing networks in terms of impedance is that nearly all the techniques that apply to resistive circuits (KVL, KCL, parallel and series combinations, Thévenin and Norton equivalents, etc.) can be extended directly to impedances. For example, the total impedance of the circuit in Figure 2.2 can be determined by using a parallel combination of the individual impedances.

Figure 2.2

$$\mathbf{Z} = \mathbf{Z}_{R} \| \mathbf{Z}_{C} = \frac{\mathbf{Z}_{R} \cdot \mathbf{Z}_{C}}{\mathbf{Z}_{R} + \mathbf{Z}_{C}} = \frac{R}{1 + j\omega CR}$$

$$= \frac{R}{\sqrt{1 + (\omega CR)^2}} \ \angle -\tan^{-1} \omega CR$$

Notice that since Z is the complex ratio of V/I, the impedance gives the magnitude and phase relationship directly.

#### Measuring Impedance Magnitude and Phase

In order to measure the impedance of a circuit or circuit element we need to determine the magnitude and phase relationship of the input voltage and input current. This measurement can be accomplished using a dual channel oscilloscope. Since the oscilloscope is a voltage measurement device, how can we use the 'scope to measure current? One way is to determine the voltage across a known circuit element (usually a resistor for convenience) and then to calculate the current via Ohm's law. Measuring the magnitude of voltages and currents is simple: just read the waveform amplitude off the 'scope display. Measuring the phase relationship is a bit more complicated since we need to see the *time* relationship between two waveforms. There are several methods to measure phase, as described below.

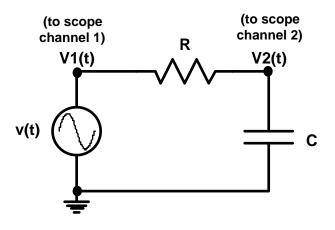

• Phase measurement using time difference

One way to measure the phase difference between two signals with the same frequency is to set the 'scope for dual trace operation, trigger on the input or reference source, and observe the time difference between the reference waveform and the waveform measured at the desired node in the circuit. This is depicted in Figure 2.3.

Figure 2.3

The phase difference between the two voltages is  $2\pi \cdot (t_d/T)$  radians, or  $360^{\circ} \cdot (t_d/T)$  degrees.

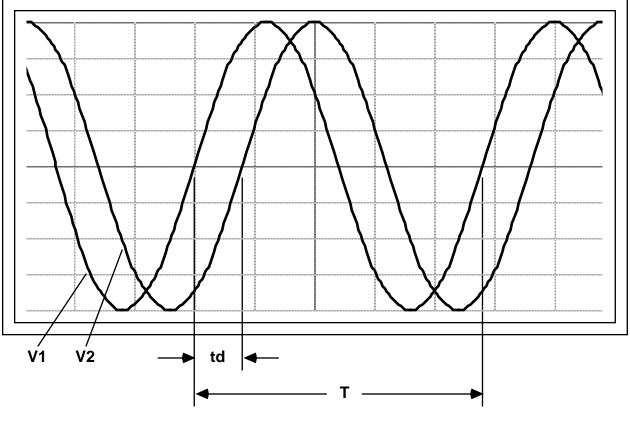

## • Phase measurement using Lissajous figures

Another way to determine the phase difference between two sinusoids is to make use of the X-Y capability of the oscilloscope. In this technique, the reference sinusoid is applied to the horizontal (X) deflection of the 'scope display while the other sinusoid is applied to the vertical (Y) deflection. Since the two waveforms have the same frequency but possibly differing phases, the resulting display will be an *ellipse*. For example, if the two waveforms are *in phase* they will both reach their maxima and minima at the same time, giving a straight diagonal line (a "squashed" ellipse). If, on the other hand, the two waveforms are 90° out of phase, the maxima and minima of one waveform always occur when the other waveform is zero, giving an ellipse with its primary axis running either horizontally or vertically depending upon the amplitude relationship of the two signals. Other phase differences give elliptical displays with various orientations. These patterns, named in honor of the French mathematician Lissajous (pronounced LEE'-ZA-SHOO'), are known as *Lissajous figures*. Several examples are shown in Figure 2.4.

Figure 2.4

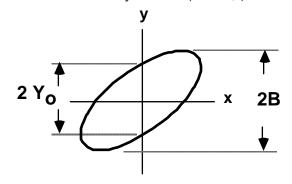

The phase difference  $\phi$  between the two signals can be determined as follows. Let  $x = A \sin \omega t$  and  $y = B \sin(\omega t + \phi)$ ,

Figure 2.5

and from Figure 2.5 we see that when x = 0,  $|y| = B \sin \phi = Y_0$ , i.e., when x = 0,  $\omega$ t must be a multiple of  $\pi$ . Therefore, the phase difference is given by

$$\sin \phi = \frac{Y_o}{B}$$

, or  $\phi = \sin^{-1} \frac{Y_o}{B}$

NOTE that if the phase difference exceeds 90° the Lissajous ellipse is tilted the other way (\), and the formula must be modified to  $\phi = 180^{\circ} - \sin^{-1} Y_{o}/B$ .

• Phase measurement using the "sum and difference" method

Still another way to determine the phase difference between two sinusoids is to make use of the *differential input* capability of the oscilloscope. The differential input mode allows the 'scope to display the sum (CH1+CH2) or difference (CH1-CH2) of the vertical trace *deflections* of the two input channels. If the vertical deflection settings (volts/div) are the same for both input channels, then the display shows the algebraic sum or difference of the two input signals in volts.

If the two input signals have the *same amplitude and frequency* but differ in phase, we can determine the phase difference as follows:

Let  $x = A \sin \omega t$  $y = A \sin(\omega t + \phi)$ , giving

$$x + y = A[\sin \omega t + \sin(\omega t + \phi)]$$

$$= A\left[\sin(\omega t - \frac{\phi}{2}) + \sin(\omega t + \frac{\phi}{2})\right]$$

$$= A\left[\sin(\omega t - \frac{\phi}{2}) - \sin(\omega t + \frac{\phi}{2})\right]$$

$$= A\left[\sin(\omega t - \frac{\phi}{2}) - \sin(\omega t + \frac{\phi}{2})\right]$$

$$= -2A\sin\frac{\phi}{2}\cos\omega t$$

Now if we measure the *amplitude* of the sum and difference signals we see that

AMPL(x + y) = "SUM" =

$$\frac{2 \operatorname{A} \cos \frac{\phi}{2}}{2}$$

and AMPL(x - y) = "DIFF"=  $\frac{2 \operatorname{A} \sin \frac{\phi}{2}}{2}$ .

Thus, the phase difference,  $\phi$ , can be obtained by observing the amplitude of the sum and difference waveforms with the 'scope, then calculating

$$\phi = 2 \cdot \tan^{-1} \left( \frac{\text{DIFF}}{\text{SUM}} \right)$$

Since the two input signals are not generally equal in amplitude, it is necessary to adjust the vertical gain so that the two signals have the same trace deflection on the 'scope screen. This is most easily accomplished by first adjusting the input (calibrated) gain settings until the two signals are approximately the same amplitude, then performing a "fine" adjustment using the continuously variable gain knob (labeled CAL). Recall that since the 'scope adds and subtracts the trace

deflections, not the absolute voltages, we can simply count the number of divisions to determine the SUM and DIFF values for use in the DIFF/SUM ratio even without the calibrated gain settings.

Question: how can the sum and difference method be used if the phase difference exceeds 90°?

#### REFERENCES

See Chapter 9 of the text by J. David Irwin, *Basic Engineering Circuit Analysis*, 4th ed., Macmillan Publishing Co., 1993 (pp. 382-424).

#### EQUIPMENT

Lab component kit Function generator

Ohm meter Oscilloscope Capacitance meter

#### PRE-LAB PREPARATION

(I) Determine the impedance of the following circuit elements at 0 Hz, 100 Hz, 1 kHz, and 10 kHz. Express the impedances in both rectangular and polar form.

a)  $100\Omega$  resistor b)  $0.1\mu$ F capacitor c) 0.3H inductor

(II) For the circuit of Figure 2.1, determine a mathematical formula for the voltage across the capacitor in terms of R, C,  $V_M$ , and  $\omega$ .

(III) Determine the phase difference between sinusoidal signals for these two different cases:

a) Sum and difference method: SUM = 7.5 units, DIFF = 1.5 units.

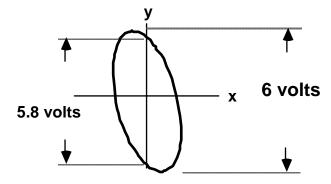

b) Lissajous method:

# EXPERIMENT

(1) Construct the series RC circuit of Figure 2.1. Use the bench function generator, a nominal  $220\Omega$  resistor and a nominal  $0.1\mu$ F capacitor. Remember to measure and record the actual values of the components used.

Choose an appropriate AC signal amplitude,  $V_M$  (large enough to display easily with the 'scope but within the power limitations of the resistor used). Setup the 'scope so that measurements of the input voltage and current can be made (or calculated easily).

Determine the magnitude and phase of the series RC impedance over at least the frequency range 200Hz thru 200kHz. NOTE that you can determine the current from measurements across the resistor using Ohm's law (i=v/R). Try a few of the measurements with each of the phase determination methods described previously to see which technique seems most convenient and reliable. Measure the impedance at enough different frequencies to determine the behavior of the impedance magnitude and phase. *Be sure* to verify the signal frequency with the oscilloscope (the markings on the function generator dial may not be extremely accurate). Also, be sure to measure the function generator output at each frequencies!

It is traditional and convenient to plot the impedance-vs.-frequency data on a *logarithmic* frequency scale (base-10). A good starting point is to measure and plot the data at an approximately equally-spaced log scale, such as 200Hz, 500Hz, 1kHz, 2kHz, 5kHz, 10kHz, etc. Note that the "1, 2, 5" spacing results in roughly equal base-10 logarithmic steps. Be sure to take additional measurements if the data plot turns up any "interesting" features (bends, peaks, etc.).

(2) Now replace the nominal  $220\Omega$  resistor with a  $1k\Omega$  resistor and again determine the impedance over the same frequency range as before. Use the phase measurement technique that you found to be the most straightforward in part 1.

#### RESULTS

(a) Prepare a plot of the impedance phase measurements made in part 1 of the experiment. Show the data as a semi-log plot: phase in degrees (linear scale) versus frequency (logarithmic scale). On the same plot show the mathematical prediction for the phase, i.e., determine the impedance of the series RC circuit. Discuss the results. Which of the phase measurements seemed to work the best for you? Why?

(b) Prepare two plots of the impedance magnitude measurements made in part 1. For the first plot, show the magnitude measurements along with the mathematical prediction as a semi-log plot: magnitude in ohms (linear scale) versus frequency (log scale). For the second plot, again show the measured and calculated magnitude values but use a log-log plot: magnitude (log scale) versus frequency (log scale). Discuss the results and compare the features of the two data plots.

(c) Prepare a plot of the impedance phase measurements (semi-log) and a plot of the impedance magnitude measurements (log-log) from part 2. On the same plots show the mathematical predictions for the impedance. Discuss the differences between the plots for part 1 and the plots for part 2.

(d) What would you change about the procedures of this experiment?

Revised 7/94

# Lab # 3 TITLE: Impedance II: Input Impedance and Active Circuits

#### ABSTRACT

The AC steady-state analysis techniques developed in the previous lab experiment are used to characterize several electronic circuits. The use of circuit simplification techniques and equivalent circuits are explored, leading to the concept of *input impedance* and *output impedance*. The description of an an active electrical circuit in terms of impedances is also introduced.

## INTRODUCTION AND THEORY

As considered in Lab #2, the sinusoidal steady-state *impedance* is defined as the complex ratio of voltage to current measured between two points within an electrical network. Furthermore, the basic circuit analysis procedures taught in EEngr 213 can be extended directly to the sinusoidal steady-state situation.

One common use of the impedance concept is in the simplification of complex electrical networks into a Thévenin equivalent impedance and voltage source. The main difference between the Thévenin circuit for a resistive network and the more general Thévenin "impedance" circuit is that the impedance varies with frequency.

#### Input Impedance

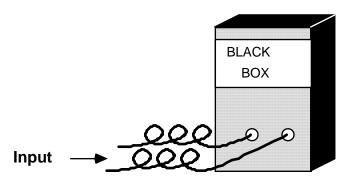

Consider the situation depicted in Figure 3.1. Here, a circuit consisting of only unknown passive linear elements (resistors, capacitors, and inductors) is contained in a "black box" that is accessible only by two wires. Let's assume that the two wires represent the *input* to the circuitry contained in the black box, e.g., the input to an audio amplifier or the connections to an electric motor.

Figure 3.1

What we really want to determine is the impedance in the box measured between the two input wires: the *input impedance*.

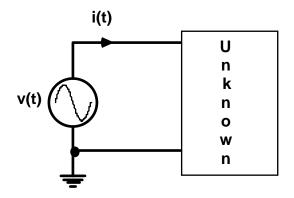

One way to determine the input impedance is to attach a known voltage source between the inputs and measure the resulting input current, as shown in Figure 3.2 (complex ratio  $Z_{in} = V_{in}/I_{in}$ ).

Figure 3.2

Measurements can be made at a range of different input frequencies if the frequency dependent characteristics of the impedance is desired. Note that in an actual measurement a series resistor is typically included so that the input current can be displayed using an oscilloscope, as in Lab #2. It it also important to note that this input impedance measurement procedure applies for PASSIVE networks only (no sources in the black box).

Output Impedance

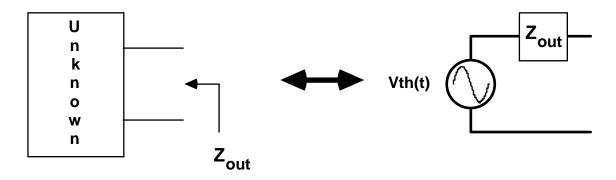

Another similar situation – but now allowing an internal sinusoidal signal source – involves determination of the *output impedance* of an electrical network. The output impedance is defined as the Thévenin impedance of the network measured between the two output connections. This concept is shown in Figure 3.3.

Figure 3.3

For example, we might be interested in determining the output impedance of a 120Vrms power outlet. Between the generating station (where  $V_{th}(t)$  is located) and the wall outlet there are likely to be miles of transmission lines, transformers, resistive losses, stray capacitances, etc. Since it is generally impractical to measure all the individual impedances between the generator and the outlet, we would rather simplify the network and lump all the effects into a *single* output impedance,  $Z_{out}$ , that can be measured directly at the outlet.<sup>\*</sup>

The Thévenin impedance (the output impedance in this case) is defined to be the complex ratio of the open circuit voltage and the short circuit current. In order to determine the Thévenin voltage we simply measure the open circuit voltage. However, the short circuit current presents several practical problems in attempting to determine the Thévenin impedance. First, we need the *phase* relationship between the voltage and current in the circuit, which means the two measurements must be made at the same time so that the relative phase can be determined. It is not possible to have both an open circuit and short circuit measurement at the same time. Second, even if we are only interested in the magnitude of the impedance and not the phase, it is often impractical to "short out" the circuit due to the large current that may flow if the output impedance is small. For example, in the 120V wall outlet mentioned in the previous paragraph, applying a short circuit to the output should cause the fuse or circuit

<sup>\*</sup> Note that although many multimeters measure resistance, they are designed for use with *passive* circuits only (a small voltage source in the meter is used to pass a current through the components under test). Hooking such a meter to an *active* circuit (like a wall outlet) in order to measure resistance is not possible and can be dangerous.

breaker protecting the branch circuit to blow, or possibly an unsafe current could flow through the wall wiring if no fuse was present.

So how can we measure the Thévenin impedance? Instead of using the short circuit current, we can make voltage and current measurements with two known load impedances attached. It is usually most convenient to use two resistors for the loads, since the voltage and current are in phase for resistances. It is important to notice that we can accomplish a similar measurement by attaching a known voltage source and measuring the resulting current for two different voltages, since the resistors we attach as loads presumably obey Ohm's law.

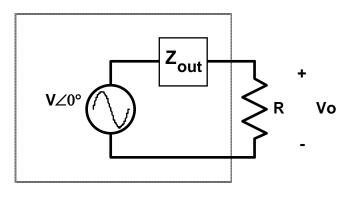

Consider the circuit of Figure 3.4. Here we assume that the Thévenin source magnitude **V** has already been determined by an open circuit voltage measurement, and the source phase is arbitrarily set to zero. Since in general we cannot have access to the components and nodes inside the dotted box, we won't be able to determine the sign (impedance phase) of  $Z_{out}$  by measuring the phase difference between **V** and **V**<sub>o</sub>.

Figure 3.4

With the known load resistor, R, attached, the magnitude of the output voltage can be expressed by the voltage division relationship

$$|\mathbf{V}_{0}| = \frac{R}{|R + Z_{out}|} |\mathbf{V}| = \frac{R}{|R + R_{out} + jX_{out}|} |\mathbf{V}|$$

$$= \frac{R}{\sqrt{\left(R + R_{out}\right)^{2} + \left(X_{out}\right)^{2}}} |\mathbf{V}|$$

Note that once we measure  $|V_0|$  we have an expression with two unknowns:  $R_{out}$  and  $X_{out}$ , the resistive and reactive parts of the output impedance, respectively. Since we have two unknowns, we need another equation to solve simultaneously. The second equation can be obtained by making a second measurement with a different known resistor attached as a load. Naming the two load resistors  $R_1$  and  $R_2$  and the corresponding output voltage measurements  $V_{o1}$  and  $V_{o2}$ , the resulting equations can be written:

$$\begin{cases} \sqrt{(R_1 + R_{out})^2 + (X_{out})^2} = R_1 \frac{|V|}{|V_{o1}|} \\ \sqrt{(R_2 + R_{out})^2 + (X_{out})^2} = R_2 \frac{|V|}{|V_{o2}|} \end{cases}$$

Squaring both sides of both equations, then subtracting, gives

$$(R_1 + R_{out})^2 - (R_2 + R_{out})^2 = \left(R_1 \frac{|\mathbf{V}|}{|\mathbf{V}_{o1}|}\right)^2 - \left(R_2 \frac{|\mathbf{V}|}{|\mathbf{V}_{o2}|}\right)^2$$

Rewriting the left side (difference of two squares) as

$$(R_1 + R_{out})^2 - (R_2 + R_{out})^2 = (R_1 + R_2 + 2R_{out}) \cdot (R_1 - R_2)$$

and solving for Rout results in:

$$R_{out} = \frac{1}{2(R_1 - R_2)} \cdot \left[ \left( R_1 \frac{|V|}{|V_{o1}|} \right)^2 - \left( R_2 \frac{|V|}{|V_{o2}|} \right)^2 \right] - \frac{(R_1 + R_2)}{2}$$

Finally, |X<sub>out</sub>| can then be determined from either of the original equations, viz.:

$$(\mathbf{X}_{\text{out}})^2 = \left(\mathbf{R}\frac{|\mathbf{V}|}{|\mathbf{V}_0|}\right)^2 - (\mathbf{R} + \mathbf{R}_{\text{out}})^2$$

If it were possible to determine the phase relationship between the Thévenin source and the output voltage we could determine the sign of  $X_{out}$ , i.e., whether the reactance was capacitive (-) or inductive (+). Can you think of any other way we could determine the sign of  $X_{out}$ ?

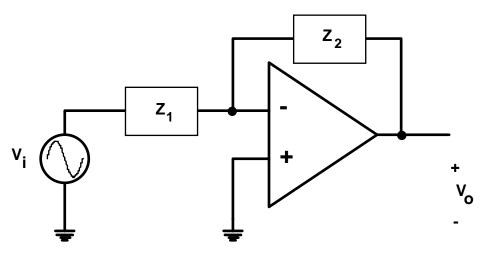

#### Impedance and Active Circuits

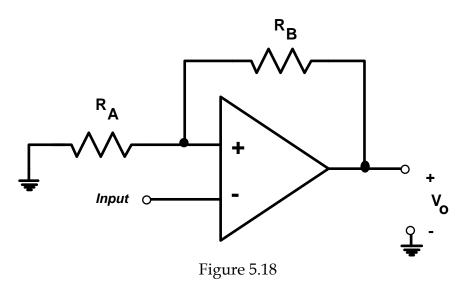

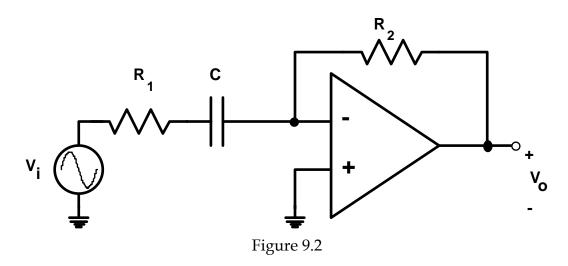

It is also possible to describe op amp circuits in terms of AC sinusoidal analysis. For example, consider the basic inverting op amp configuration shown in Figure 3.5.

Figure 3.5

Analysis of this circuit using the basic ideal op amp properties considered in EEngr 213 shows that the phasor relationship for the circuit is given by

$$\mathbf{V}_{\mathrm{o}} = -\frac{\mathbf{Z}_{2}}{\mathbf{Z}_{1}}\mathbf{V}_{\mathrm{i}}$$

It is also possible to determine the input impedance and output impedance for the circuit. The input impedance  $(V_i/I_i)$  is simply  $Z_1$  because the input voltage appears entirely across  $Z_1$  (the inverting op amp input is held at ~0 volts). The output impedance is *zero*, since the output impedance of the op amp (ideal) is itself zero (the parallel combination of zero with anything else is still zero)! Of course, a real op amp is not completely ideal so the input and output impedances only approach the ideal values.

#### REFERENCES

See Chapter 9 of the text by J. David Irwin, *Basic Engineering Circuit Analysis*, 4th ed., Macmillan Publishing Co., 1993 (pp. 382-424).

#### EQUIPMENT

Lab component kit Function generator

Ohm meter Oscilloscope

Capacitance meter

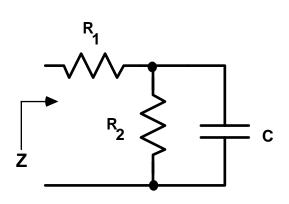

PRE-LAB PREPARATION

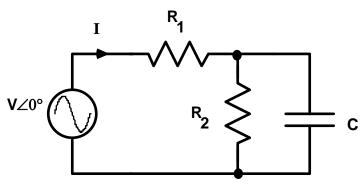

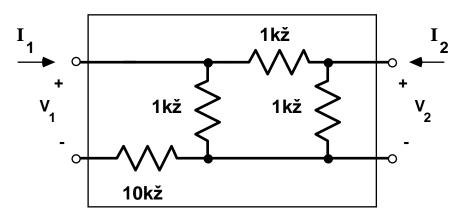

Figure 3.6

(I) Determine an expression for the input impedance of the series-parallel network in Figure 3.6. What is the input impedance (magnitude and phase) for low frequencies ( $\omega \oslash 0$ ) and for high frequencies ( $\omega \oslash \Box$ )?

(II) The circuit of Figure 3.6 is attached to a sinusoidal voltage source, as shown in Figure 3.7. The circuit is configured with:  $|\mathbf{V}| = 1$  volt,  $\omega = 2\pi \cdot (10 \text{kHz})$ ,  $R_1=1 \text{k}\Omega$ , and  $R_2=10 \text{k}\Omega$ . The value of the capacitor is unknown, but the amplitude of the voltage across the capacitor is measured to be 0.707 volts. From this single measurement, determine the value of the capacitance and the expected phase difference between the input voltage waveform and the input current waveform.

Figure 3.7

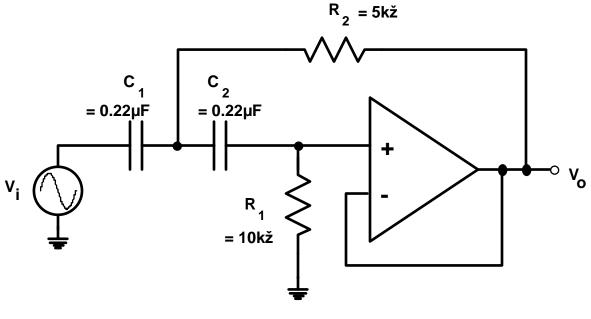

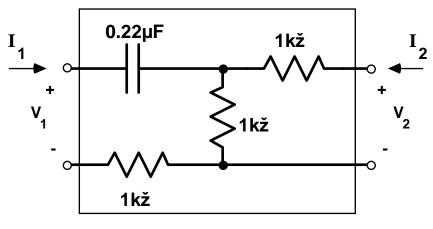

(III) What is voltage gain expression  $(V_0/V_i)$  for the circuit of Figure 3.8? Assume an ideal op amp. Calculate the magnitude and phase of the gain expression for frequencies from 10Hz to 100kHz using a "1, 2, 5,..." frequency sequence (use a computer program or MAPLE, if you wish). Finally, use PSpice to perform an AC analysis of the circuit over the 10Hz - 100kHz range. Use the PSpice ua741 op amp model. Plot the PSpice magnitude results on a log scale with a log frequency axis.

Figure 3.8

# EXPERIMENT

(1) Assemble the circuit of Figure 3.7 using the function generator as the source and the nominal component values  $R_1 = 1k\Omega$ ,  $R_2 = 10k\Omega$ , and  $C = 0.1\mu$ F. Make measurements of the impedance magnitude and phase at enough frequencies to fully describe the behavior of the circuit.

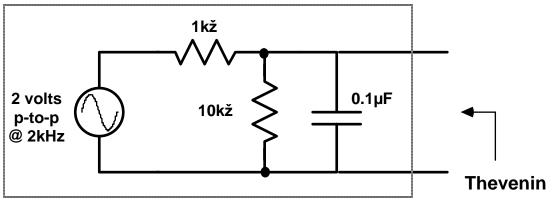

(2) Now assume that the circuit of Figure 3.7 is an *unknown* circuit that you can access only via two wires, as show in Figure 3.9 below. Set the generator for 2 volts peak-to-peak at 2kHz. Using the "load resistor" approach described in the lab introduction, make external measurements of your choice to come up with an estimate of the Thévenin equivalent circuit for the network as observed from the external connections.

Figure 3.9

(3) Assemble the circuit of Figure 3.8 using the indicated nominal component values. Measure the complex voltage gain  $(V_0/V_i)$ , both magnitude and phase, over the frequency range 10Hz thru 100kHz. Take sufficient measurements to fully describe the behavior of the circuit.

## RESULTS

(a) Prepare a plot of the impedance magnitude and phase using the measurements of part 1. Also plot the theoretical prediction of the impedance using the measured component values in the mathematical expression for the impedance developed in the pre-lab. Use a log scale for the frequency axis, plot the magnitudes on a log scale, and plot the phases on a linear scale. Discuss the results.

(b) What load resistor values did you use in your measurements for part 2? Compare your measured Thévenin impedance results to a theoretical prediction based on the known circuit configuration.

(c) Plot your magnitude and phase measurements of the voltage gain from part 3 and compare with the mathematical expression (ideal op amp) and PSpice results from the prelab. Again, use a magnitude (log axis) vs. frequency (log axis) plot.\* How would you describe the agreement between the measurements and the predictions?

(d) How would you modify this experiment to make it more useful to you?

Revised 7/94

<sup>&</sup>lt;sup>\*</sup> Incidentally, this form of plot (log gain vs. log frequency) is referred to as a *Bode* (Boh-dee) plot, named after the engineer H. W. Bode.

# Lab # 4 TITLE: Terminal Characteristics of Semiconductor Diodes

### ABSTRACT

The *diode* is the most commonly encountered nonlinear circuit element. This experiment involves measurements of the voltage and current behavior of a semiconductor diode, and the behavior of several electrical networks involving resistors and diodes. The measured results are compared to SPICE simulations and hand analysis using elementary diode models.

## INTRODUCTION AND THEORY

Like resistors, inductors, and capacitors, the semiconductor diode is a passive twoterminal device. But unlike R, L, and C, the diode is a *nonlinear* circuit element, meaning that the relationship between voltage and current in the diode will not be linear in a mathematical sense. This means that some of our basic circuit analysis techniques, such as superposition and proportionality, will *not* be applicable to diode circuits. The implications of nonlinear circuit analysis will be explored in this and subsequent experiments.

### Characteristics of Diode Behavior

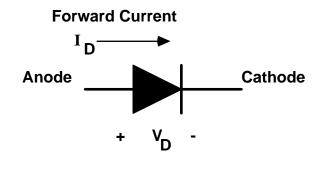

The diode is a physical approximation to a unidirectional wire: an ideal diode would be a perfect conductor for one direction of current through the device, and a perfect insulator for current attempting to flow in the other direction. Such an ideal device could also be described as having zero impedance in one direction and infinite impedance in the other direction. The schematic symbol for a diode is depicted in Figure 4.1a. Forward (positive) current enters at the *anode* of the device and exits at the *cathode*.

Figure 4.1a

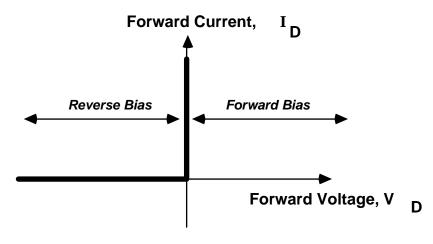

If the circuit attached to the diode results in current through the diode in the *forward* direction (with the arrow) the diode is said to be *forward biased*, or simply *ON*. If the circuit attached to the diode attempts to force current in the reverse direction, the diode is said to be *reverse biased*, or *OFF*. A plot of the terminal characteristics (current vs. voltage) for an ideal diode is shown in Figure 4.1b.

Figure 4.1b

Note that if it were possible to construct an ideal diode, it would conduct any amount of current with zero voltage drop (vertical line on V=0, I>0 axis) and zero current with any amount of reverse bias voltage (horizontal line on I=0, V<0 axis). Although such an ideal device does not exist, the ideal diode concept is useful in performing a quick "eyeball" analysis of a real diode circuit.

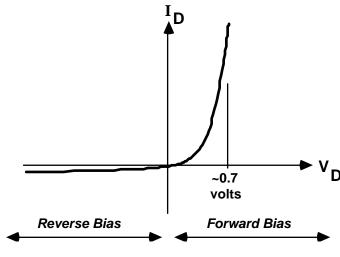

A real semiconductor diode (or *junction diode*<sup>\*</sup>) has terminal characteristics which differ from the ideal case in several respects, as shown in Figure 4.2. A semiconductor diode

<sup>&</sup>lt;sup>\*</sup> The term *junction* diode comes from the fact that the diode is constructed as a metallurgical junction between two materials with different electrical properties, such as p- and n-type semiconductors.

fabricated from silicon materials requires a forward bias of approximately 0.7 volts before the device conducts appreciably in the forward direction. In the reverse direction the diode conducts a small *leakage* current that is usually much smaller than the forward current. The junction diode is typically composed of a *pn junction*, meaning that *p*-type and *n*-type semiconductor materials are fabricated in direct contact with each other. The anode of the device is *p*-type material and the cathode is *n*-type. Thus, the *forward* current through the device is in the direction from *p* to *n*.

Analysis of the physical mechanisms for current conduction across semiconductor junctions (considered in EEngr 315, etc.) gives a theoretical description of the voltage and current relationship in a real junction diode:

$$I_{D} = I_{s} \left( e^{\frac{V_{D}}{nV_{T}}} - 1 \right)$$

where

I<sub>D</sub> and V<sub>D</sub> are the diode current and voltage as defined in Figure 4.1,

I<sub>s</sub> is the *scale current*,

V<sub>T</sub> is the *thermal voltage*,

n is a constant between 1 and 2.

and **n** is a constant between 1 and 2.

Figure 4.2

The scale current I<sub>s</sub> is a constant for a particular diode at a fixed temperature, but varies with the size and temperature of the junction. Typical values of I<sub>s</sub> for small diodes are in the range of  $10^{-13}$  to  $10^{-15}$  amps. V<sub>T</sub>, the thermal voltage, is defined as kT/q, where k

is Boltzmann's constant (1.38x10<sup>-23</sup> joules/kelvin), *T* is the absolute temperature in kelvin, and *q* is the charge of an electron (1.602x10<sup>-19</sup> coulomb). Near room temperature V<sub>T</sub> is approximately 25mV. Finally, the constant *n* ( $1 \le n \le 2$ ) depends upon the material used to make the diode and the physical geometry of the device.

The diode equation predicts that the reverse current (current flowing under reverse bias conditions) should be equal to I<sub>s</sub>. In a real diode, however, additional *leakage* current is usually present due to the packaging of the diode and other effects so that the reverse current may be many times greater than predicted by semiconductor theory.

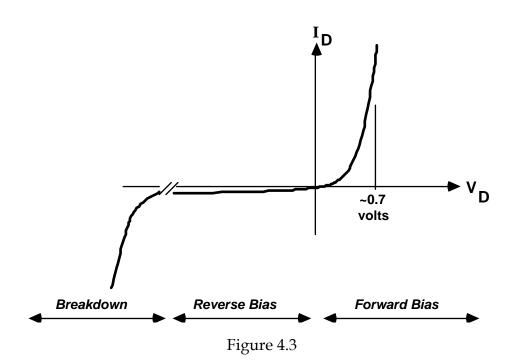

If the reverse voltage is increased above some particular value the diode will exhibit *reverse breakdown*. In the breakdown region the diode no longer behaves as an open circuit, and appreciable current may flow in the reverse direction through the device. This behavior is sketched in Figure 4.3. <u>Although operation in the breakdown region is not necessarily damaging to the diode</u>, the *power dissipation* (I<sub>reverse</sub>  $\cdot$  V<sub>reverse</sub>) must be limited so that the device does not burn up.

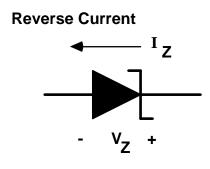

### Zener Diodes

Some diodes are designed specifically to operate in the breakdown region. These devices are called *breakdown diodes*, or more commonly *Zener diodes* (ZEE-NUR), named for a semiconductor researcher. Zener diodes are designed to have a very abrupt

transition from the reverse bias region to the breakdown region and a very steep slope (current vs. voltage) in the breakdown region. This allows the Zener diode to be a good voltage reference when operated in the breakdown region (holding an essentially constant voltage for small variations in current). Zener diodes behave like "regular" diodes when operated in the forward bias region. Zeners are available with breakdown voltages from a few volts to a few tens of volts. The symbol for a Zener diode is shown in Figure 4.4.

Figure 4.4

Note that the voltage and current specifications for Zeners are usually given for the *reverse* direction, i.e., operation in the breakdown region. The power dissipation rating for Zener diodes must be obeyed to prevent damage to the device. This usually means the inclusion of a series resistance in the circuit to limit the Zener current in the breakdown region.

### Diode Specifications

Ordinary junction diodes can be classified roughly into two general types: *switching* diodes for use in low-power signal processing applications, and *power* diodes for use in electrical power circuits. Discrete diodes are rated by manufacturers using several parameter specifications, as summarized below.

- *Maximum forward average current* (*I*<sub>*F*(*AV*)</sub>) this specification indicates the allowable average current the device is designed to handle without being damaged. A *peak* or *surge* current rating is sometimes also given, indicating the maximum current capability of the device for a short period of time (usually a few milliseconds at most).

- *Maximum peak reverse voltage* ( $V_{R(PEAK)}$ ) or *peak inverse voltage* (*PIV*) this specification gives the maximum voltage that can be applied in the reverse

direction across the diode. Exceeding this voltage can result in diode breakdown, which means that appreciable current will start to flow in the reverse direction through the device.

- *Maximum forward voltage at specified current (V<sub>F(MAX)</sub> @ I<sub>F</sub>)* the forward voltage at a specified current identifies how much voltage drop we can expect across the diode when conducting in the forward direction. Sometimes a diode is referred to as an "X milliamp diode", where X is the nominal forward current when the diode voltage is 0.7 volts.

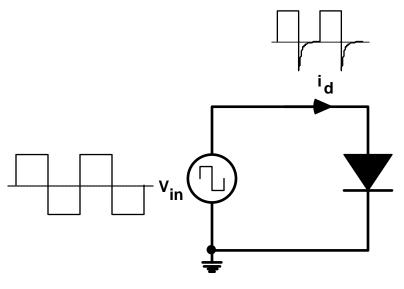

- *Reverse recovery time*  $(t_{rr(max)})$  when the diode is switched suddenly from the forward conduction state to the reverse blocking state a large reverse current is often observed for tens or hundreds of nanoseconds  $(t_{rr(max)})$  before the diode begins to block the reverse current. This effect is due to the finite time required to move the charge carriers (electrons and holes) at the semiconductor junction. The reverse recovery effect is most noticeable for diodes with large junction area when switching state (on to off) in a rapid fashion, as depicted in Figure 4.5.

Figure 4.5

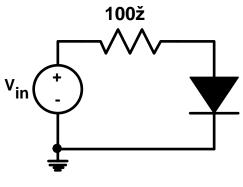

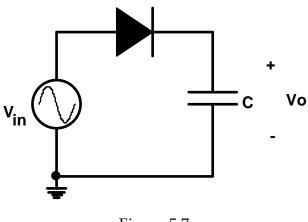

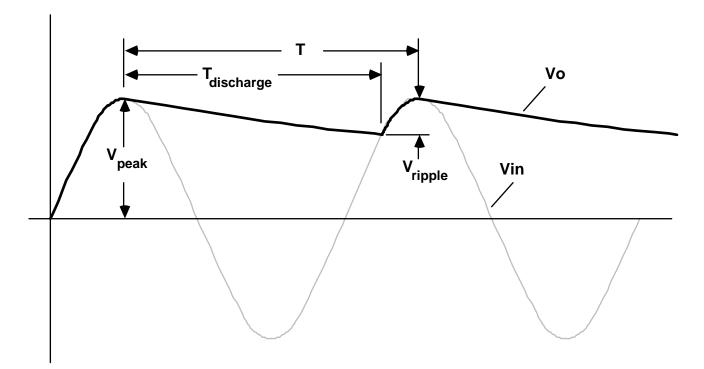

#### Diode Rectifiers

Diodes are used in numerous important applications in electrical engineering. Some of the most common applications are in *rectification*. Rectification allows an AC input signal (zero average value) to be converted to a time varying signal with a DC component (nonzero average value). This process is needed for using an AC power line

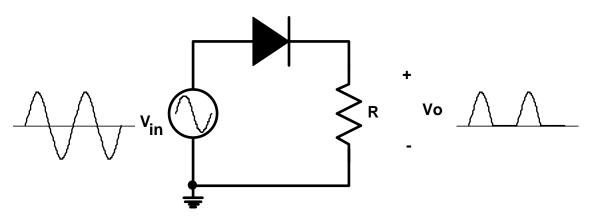

voltage to supply a DC voltage in a power supply. Consider the circuit of Figure 4.6. In this example the alternating voltage source attempts to create an alternating current in the loop.

When the voltage at the source is positive, current will tend to flow through the diode in the forward direction, through the resistor, and back to the source. However, when the voltage at the source becomes negative, current would have to flow in the *reverse* direction through the diode, which is not possible. Since only current in the positive direction is allowed through the resistor the output voltage is only positive. This circuit performs *half-wave rectification* because only half of the input waveform appears at the load resistor. Because a real junction diode has a non-zero forward voltage when conducting ( $V_D \approx 0.7$  volts), the output voltage will be less than the input voltage ( $V_{o,}$ peak =  $V_{in}$ , peak -  $V_D$ ).

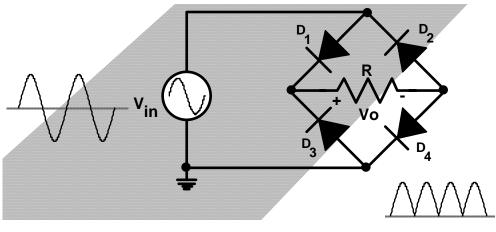

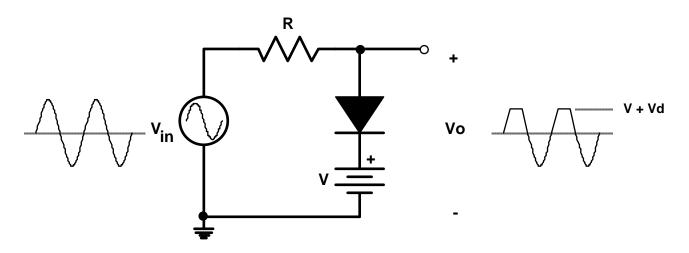

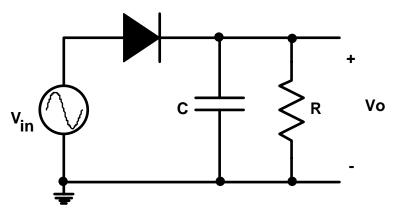

It is possible to create a *full-wave rectifier* using a diode *bridge* circuit, as shown in Figure 4.7.

Figure 4.7

For positive source voltages the current flows through D<sub>1</sub>, through the load resistor from left to right, through D<sub>4</sub>, and back to the source (D<sub>2</sub> and D<sub>3</sub> are reverse biased and do not conduct). Similarly, when the source voltage goes negative the current is induced to flow through D<sub>3</sub>, through the load *again from left to right*, through D<sub>2</sub>, and back to the source. Thus, the current flows through the load in the same direction for both positive and negative input voltages, i.e., the *full-wave* is rectified. Note that a fullwave rectifier constructed as a diode bridge has a *floating load*, that is, the load resistor cannot be connected to the ground reference of the source (this would place a short circuit across one of the bridge diodes). Also notice that the voltage across the load is less than the input voltage by *two* diode "on" voltages since the load current must flow through two diodes.

## Diodes and SPICE

SPICE includes a built-in diode model. The model implements the basic junction diode equation, except SPICE uses the symbol **IS** for  $I_s$ , and **N** for n. A diode is declared in SPICE as:

```

Dname +node -node modelname

...

.MODEL modelname D (IS=xx, N=yy),

```

where *+node* and *-node* are the node numbers connected to the anode and cathode of the diode, respectively. The name of the diode (*Dname*) is up to you, except that the first letter must be a D. You are also free to choose the name of the model.

The SPICE diode model also has numerous other parameters besides the basic diode equation. For example, the SPICE diode can simulate operation in the breakdown region, if desired.

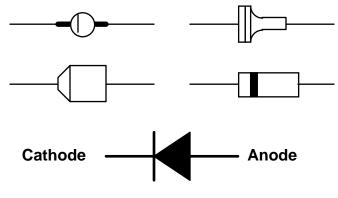

### Diode Packaging

Discrete diodes come in various shapes and sizes. The smallest discrete diodes are similar in size to 1/4-watt resistors, but are usually black in color or constructed from glass or colored plastic. The cathode of the diode is typically indicated by a wide band or some other marking, as shown in Figure 4.8. Power diodes are generally larger in size, and are often equipped with a large metal flange to allow the device to be physically mounted on a heat sink. Of course, it is always possible to verify the polarity of the diode simply by testing: The diode should conduct negligible current when in reverse bias and an approximately fixed voltage drop in the forward bias direction. Diodes are often given a standard part number beginning with '1N', e.g., 1N4001, 1N251, etc.

Figure 4.8

It is also possible to purchase bridge diode circuits consisting of several diodes mounted in a single package. These devices simplify the layout and assembly of rectifier circuits by reducing the number of individual components that must be handled.

### REFERENCES

See Chapter 3 of the text by Sedra and Smith, *Microelectronic Circuits*, 3rd ed., Saunders College Publishing (Holt, Rinehart, and Winston), 1991 (pp. 116-190).

*SPICE User's Guide,* (available from UNL IEEE Student Branch)

Paul W. Tuinenga, *SPICE: A Guide to Circuit Simulation and Analysis Using PSpice*, 2nd Ed., Prentice-Hall, 1992.

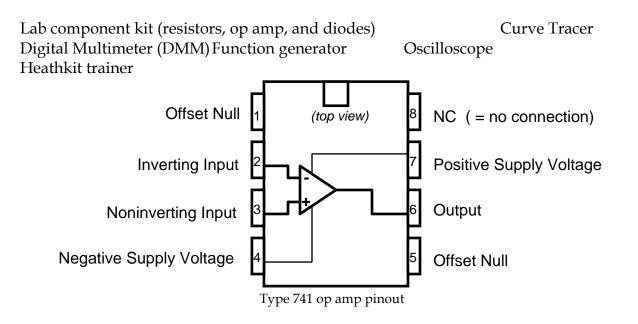

#### EQUIPMENT

### PRE-LAB PREPARATION

(I) A diode is connected in a circuit under forward bias conditions. Two measurements of the diode voltage and current are:

0.63 volts @ 10.1mAand0.71 volts @ 110mAFrom these measurements calculate the value of  $I_s$  and n for this diode. Assume the thermal voltage,  $V_T$ , is 25mV.

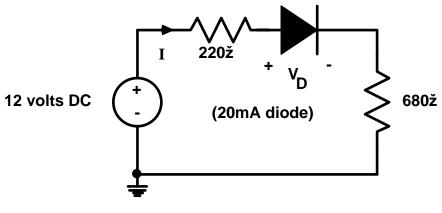

(II) A 20mA diode ( $V_D = 0.7$  volts when  $I_D = 20mA$ ) is known to have n=2. Use iteration or some other method and the junction diode equation to solve for the unknown loop current and diode voltage in the circuit of Figure 4.9 below. Also, simulate the circuit using SPICE and compare the results to your hand analysis.

Figure 4.9

(III) A half-wave rectifier circuit is constructed as shown in Figure 4.6. Use an "ideal" diode model (short circuit for forward current, open circuit for reverse voltage). Using a 120V rms input sinusoid and R=10 $\Omega$ , calculate the *peak* forward current and *peak* reverse voltage for the diode, the *average* forward current in the diode, and the *rms* power dissipated in the resistor. Recall that the average of a periodic signal, x(t), with

period T is defined  $\frac{1}{T} \int_{t_o}^{t_o+T} x(t) dt$ , while the rms value is defined  $\sqrt{\frac{1}{T} \int_{t_o}^{t_o+T} x^2(t) dt}$

(IV) Repeat the calculations of (III) but now use a 2V rms input sinusoid and assume a simple 0.7V model for the diode ( $V_D = 0.7$  volts for forward current,  $I_D = 0$  for reverse voltage). Also, use SPICE with a 5mA, n=1.5 diode model to simulate the output waveform for a 60Hz input frequency.

### EXPERIMENT

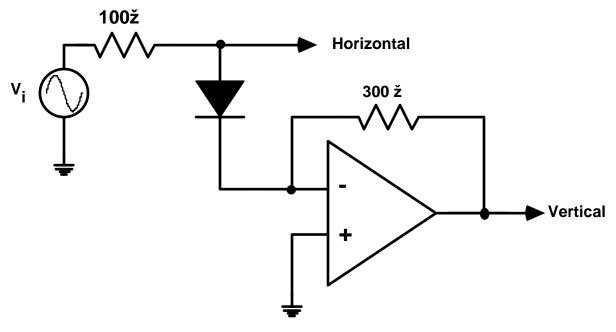

(1) First, consider how we might use the oscilloscope to display the current vs. voltage characteristic for the junction diode. In order to do this we must be able to display the diode voltage, V, on the horizontal axis of the 'scope and the diode current, I, on the vertical axis. Thus, the 'scope should be set up in XY mode. The circuit in Figure 4.10 shows one way to display the diode current as a voltage on the 'scope screen.

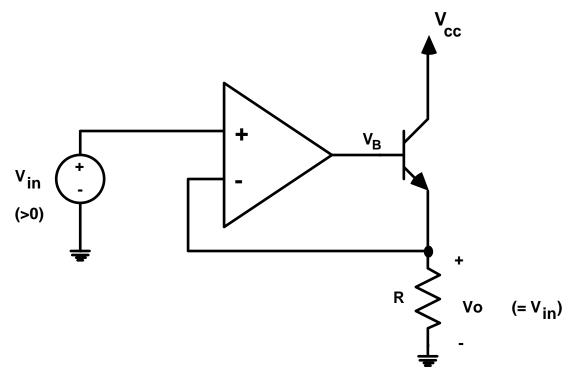

Figure 4.10

The operational amplifier forces the cathode of the diode to be held at approximately zero volts. Thus, the voltage measured at the anode of the diode is, in fact, the diode voltage, V<sub>D</sub>. Noting that the diode current flows through the  $300\Omega$  feedback resistor, the op amp output voltage is given by -300 I<sub>D</sub>. Thus, the output voltage of the op amp is directly proportional to the diode current, I<sub>D</sub>. The oscilloscope can now be used to display the diode characteristic. *NOTE* that this technique is limited by the output current capability of the op amp, typically 25 - 50 mA.

Assemble the circuit of Figure 4.10 using the trainer breadboard. Carefully record the voltage and current measurements made from the 'scope screen, and also sketch the displayed diode characteristic. Can you think of any other way to use the 'scope to display the diode I vs. V curve?

Next, use the *curve tracer* instrument in the lab to produce the I vs. V curve for the diode. Obtain a printout of the results, if possible.

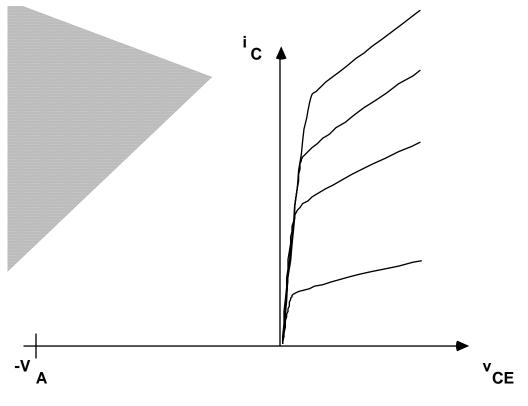

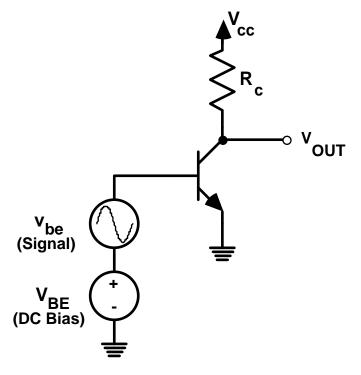

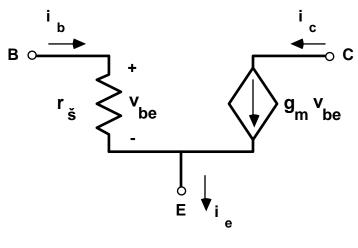

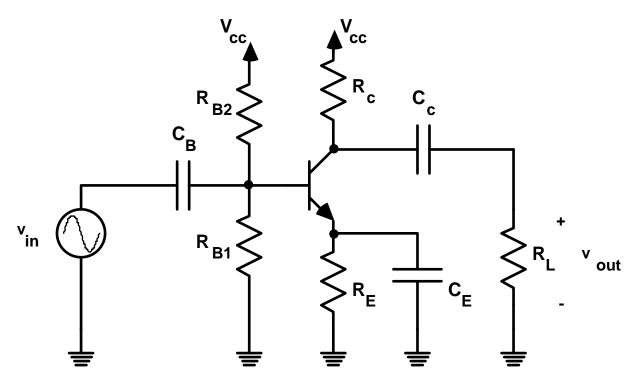

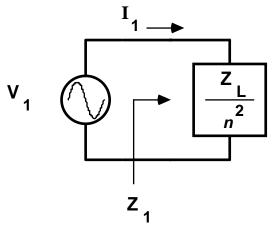

(2) Now carefully measure the diode voltage and current using the DMM with the circuit of Figure 4.11 over the range  $-10 < V_{in} < +10$  volts. Make sufficient measurements to produce a reasonable plot of the characteristic to compare with the 'scope and curve tracer measurements. Use the measurements to deduce the value of Is and the product nV<sub>T</sub>. To avoid the complication of the internal resistance of the